## NEHRU COLLEGE OF ENGINEERING AND RESEARCH CENTRE (NAAC Accredited)

(Approved by AICTE, Affiliated to APJ Abdul Kalam Technological University, Kerala)

#### DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

### **COURSE MATERIALS**

### CS 207 ELECTRONIC DEVICES & CIRCUITS

#### VISION OF THE INSTITUTION

To mould true citizens who are millennium leaders and catalysts of change through excellence in education.

#### MISSION OF THE INSTITUTION

**NCERC** is committed to transform itself into a center of excellence in Learning and Research in Engineering and Frontier Technology and to impart quality education to mould technically competent citizens with moral integrity, social commitment and ethical values.

We intend to facilitate our students to assimilate the latest technological know-how and to imbibe discipline, culture and spiritually, and to mould them in to technological giants, dedicated research scientists and intellectual leaders of the country who can spread the beams of light and happiness among the poor and the underprivileged.

#### ABOUT DEPARTMENT

♦ Established in: 2002

♦ Course offered: B.Tech in Computer Science and Engineering

M.Tech in Computer Science and Engineering

M.Tech in Cyber Security

♦ Approved by AICTE New Delhi and Accredited by NAAC

◆ Affiliated to the University of A P J Abdul Kalam Technological University.

#### **DEPARTMENT VISION**

Producing Highly Competent, Innovative and Ethical Computer Science and Engineering Professionals to facilitate continuous technological advancement.

#### **DEPARTMENT MISSION**

- 1. To Impart Quality Education by creative Teaching Learning Process

- 2. To Promote cutting-edge Research and Development Process to solve real world problems with emerging technologies.

- 3. To Inculcate Entrepreneurship Skills among Students.

- 4. To cultivate Moral and Ethical Values in their Profession.

5.

#### PROGRAMME EDUCATIONAL OBJECTIVES

- **PEO1:** Graduates will be able to Work and Contribute in the domains of Computer Science and Engineering through lifelong learning.

- **PEO2:** Graduates will be able to Analyse, design and development of novel Software Packages, Web Services, System Tools and Components as per needs and specifications.

- **PEO3:** Graduates will be able to demonstrate their ability to adapt to a rapidly changing environment by learning and applying new technologies.

- **PEO4:** Graduates will be able to adopt ethical attitudes, exhibit effective communication skills, Teamworkand leadership qualities.

#### **PROGRAM OUTCOMES (POS)**

### **Engineering Graduates will be able to:**

- 1. **Engineering knowledge**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- 2. **Problem analysis**: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- 3. **Design/development of solutions**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- 4. **Conduct investigations of complex problems**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- 5. **Modern tool usage**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- 6. **The engineer and society**: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- 7. **Environment and sustainability**: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- 8. **Ethics**: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- 9. **Individual and team work**: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- 10. **Communication**: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- 11. **Project management and finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- 12. **Life-long learning**: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

### PROGRAM SPECIFIC OUTCOMES (PSO)

**PSO1**: Ability to Formulate and Simulate Innovative Ideas to provide software solutions for Real-time Problems and to investigate for its future scope.

**PSO2**: Ability to learn and apply various methodologies for facilitating development of high quality System Software Tools and Efficient Web Design Models with a focus on performance

optimization.

**PSO3**: Ability to inculcate the Knowledge for developing Codes and integrating hardware/software products in the domains of Big Data Analytics, Web Applications and Mobile Apps to create innovative career path and for the socially relevant issues.

### **COURSE OUTCOMES**

| CO1 | To introduce to the students the fundamental concepts of electronic devices and circuits for engineering applications. |

|-----|------------------------------------------------------------------------------------------------------------------------|

| CO2 | To develop the skill of analysis and design of various analog circuits using electronic devices                        |

| CO3 | To provide comprehensive idea about working principle, operation and applications of electronic circuits               |

| CO4 | To equip the students with a sound understanding of fundamental concepts of operational amplifiers                     |

| CO5 | To expose to the diversity of operations that operational amplifiers can perform in a wide range of applications       |

| CO6 | To expose to a variety of electronic circuits/systems using various analog ICs                                         |

### MAPPING OF COURSE OUTCOMES WITH PROGRAM OUTCOMES

|     | PO | PO | РО | PO | PO | PO | PO | PO | РО | P      | PO | PO |

|-----|----|----|----|----|----|----|----|----|----|--------|----|----|

|     | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 0      | 11 | 12 |

|     |    |    |    |    |    |    |    |    |    | 1<br>0 |    |    |

| CO1 | 3  |    | 3  | 2  | 2  | 2  |    |    | 2  |        |    |    |

| CO2 | 3  | 3  | 3  | 2  | 2  | 2  |    |    | 2  | ,      |    |    |

| CO3 | 3  | 3  | 3  | 2  | 2  | 2  |    |    | 2  |        |    |    |

| CO4 | 3  | 3  | 3  | 2  | 2  | 2  |    |    | 2  |        |    |    |

| CO5 | 3  | 3  | 3  | 2  | 2  | 2  |    |    | 2  |        |    |    |

| CO6 | 3  | 3  | 3  | 2  | 2  | 2  |    |    | 2  |        |    |    |

Note: H-Highly correlated=3, M-Medium correlated=2, L-Less correlated=1

#### PSO MAPPINGS ALSO NEEDS TO INCLUDE

| CO'S   | PSO1 | PSO2 | PSO3 |

|--------|------|------|------|

| C205.1 | 3    | 3    | 2    |

| C205.2 | 3    | 3    | 2    |

| C205.3 | 3    | 3    | 2    |

| C205.4 | 3    | 3    | 2    |

| C205.5 | 3    | 3    | 2    |

| C205.6 | 3    | 3    | 2    |

#### **SYLLABUS**

| Course code | Course Name                   | L-T-P -Credits | Year of<br>Introduction |

|-------------|-------------------------------|----------------|-------------------------|

| CS207       | ELECTRONIC DEVICES & CIRCUITS | 3-0-0-3        | 2016                    |

#### Pre-requisite: BE101-04 Introduction to Electronics Engg.

#### Course Objectives:

- To introduce to the students the fundamental concepts of electronic devices and circuits for engineering applications

- To develop the skill of analysis and design of various analog circuits using electronic devices

- To provide comprehensive idea about working principle, operation and applications of electronic circuits

- To equip the students with a sound understanding of fundamental concepts of operational amplifiers

- To expose to the diversity of operations that operational amplifiers can perform in a wide range of applications

- To expose to a variety of electronic circuits/systems using various analog ICs

#### Syllabus

RC Circuits, Diode Circuits, Regulated power supplies, Field effect transistor, DC analysis of BJT, RC Coupled amplifier, MOSFET amplifiers, Feedback amplifiers, Power amplifiers, Oscillators, Multivibrators, Operational Amplifier and its applications, Timer IC.

#### Expected Outcome:

Students will be able to

- explain, illustrate, and design the different electronic circuits using electronic components

- design circuits using operational amplifiers for various applications

#### Text Books:

- 1. David A Bell, Electronic Devices and Circuits, Oxford University Press, 2008

- Salivahanan S. and V. S. K. Bhaaskaran, Linear Integrated Circuits, Tata McGraw Hill, 2008

#### References:

- Neamen D., Electronic Circuits, Analysis and Design, 3/e, TMH, 2007

- Robert Boylestad and L Nashelsky, Electronic Devices and Circuit Theory, Pearson.

- 3. Bogart T. F., Electronic Devices Circuits, 6/e, Pearson, 2012.

- 4. Maini A. K. and V. Agrawal, Electronic Devices and Circuits, Wiley India, 2011.

- 5. K.Gopakumar, Design and Analysis of Electronic Circuits, Phasor Books, Kollam, 2013

- 6. Millman J. and C. Halkias, Integrated Electronics, 2/e, McGraw-Hill, 2010.

|        | Course Plan                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                      |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|--|

| Module | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Hou<br>1'S<br>(40) | Sem<br>Exam<br>Marks |  |

| 1      | Wave shaping circuits: Sinusoidal and non-sinusoidal wave shapes, Principle and working of RC differentiating and integrating circuits, Conversion of one non-sinusoidal wave shape into another.  Clipping circuits - Positive, negative and biased clipper.                                                                                                                                                                                                              | 5                  | 15%                  |  |

|        | Clamping circuits - Positive, negative and biased clamper.  Voltage multipliers- Voltage doubler and tripler.  Simple sweep circuit using transistor as a switch.                                                                                                                                                                                                                                                                                                          |                    |                      |  |

| 2      | Regulated power supplies: Review of simple zener voltage regulator, Shunt and series voltage regulator using transistors, Current limiting and fold back protection, 3 pin regulators-78XX and 79XX, IC 723 and its use as low and high voltage regulators, DC to DC conversion, Circuit/block diagram and working of SMPS.                                                                                                                                                | 4                  | 15 %                 |  |

|        | Field effect transistors: JFET – Structure, principle of operation and characteristics, Comparison with BJT.  MOSFET- Structure, Enhancement and Depletion types, principle of operation and characteristics.                                                                                                                                                                                                                                                              | _3                 |                      |  |

|        | FIRST INTERNAL EXAM                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |                      |  |

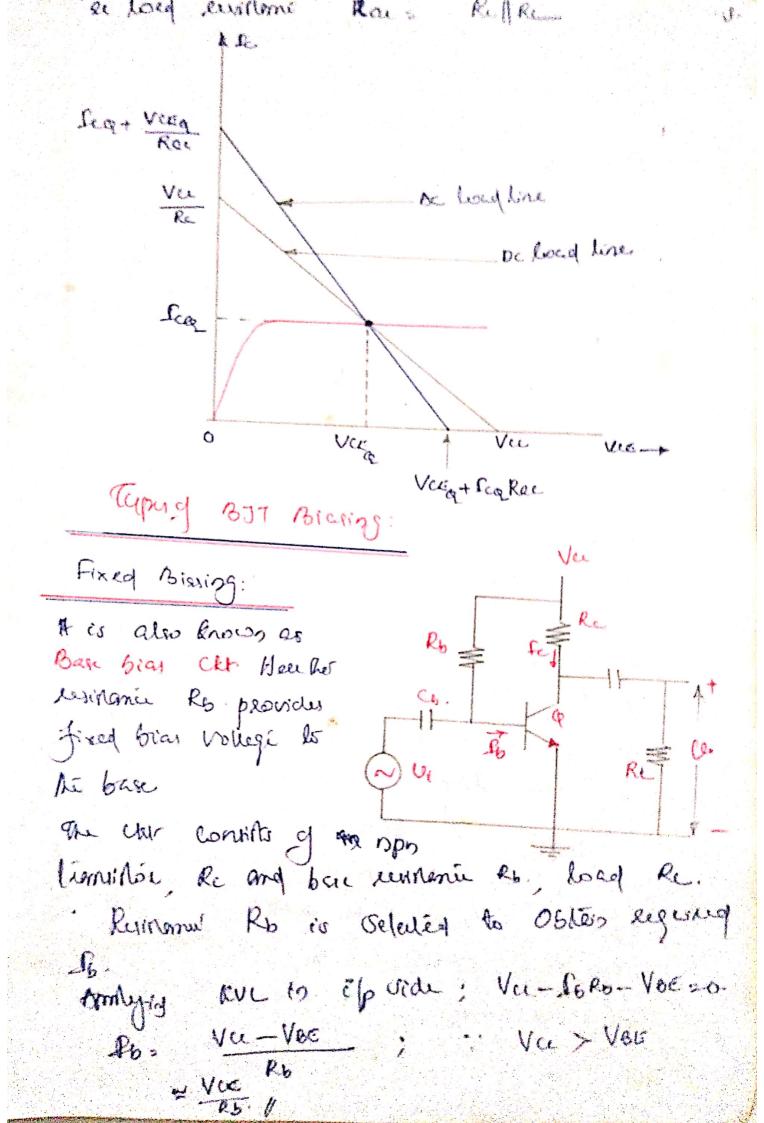

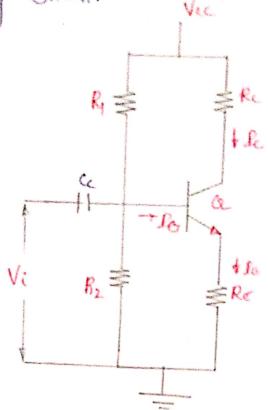

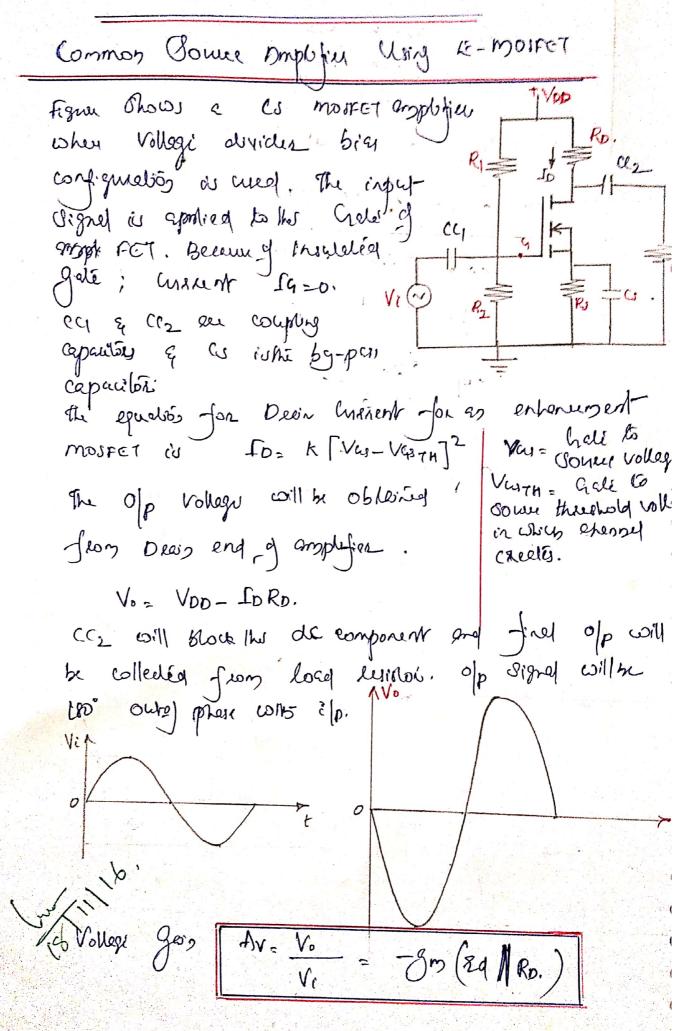

| 3      | Amplifiers: Introduction to transistor biasing, operating point, concept of load line, thermal stability, fixed bias, self bias, voltage divider bias. Classification of amplifiers, RC coupled amplifier - voltage gain and frequency response. Multistage amplifiers - effect of cascading on gain and bandwidth.  Feedback in amplifiers - Effect of negative feedback on amplifiers.  MOSFET Amplifier- Circuit diagram and working of common source MOSFET amplifier. | 7                  | 15 %                 |  |

| 4 | Oscillators: Classification, criterion for oscillation, analysis of Wien bridge oscillator, Hartley and Crystal oscillator.  Non-sinusoidal oscillators: Astable, monostable and bi-stable multivibrators using transistors (Only design equations and working of circuit are required, Analysis not required).                                                                                                                                                                    | 5 | 15 % |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|

|   | SECOND INTERNAL EXAM                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |

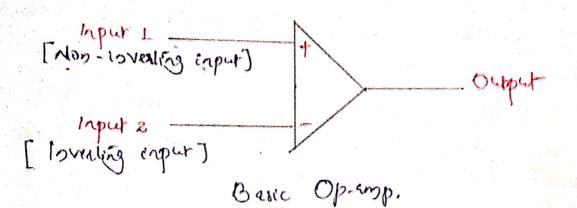

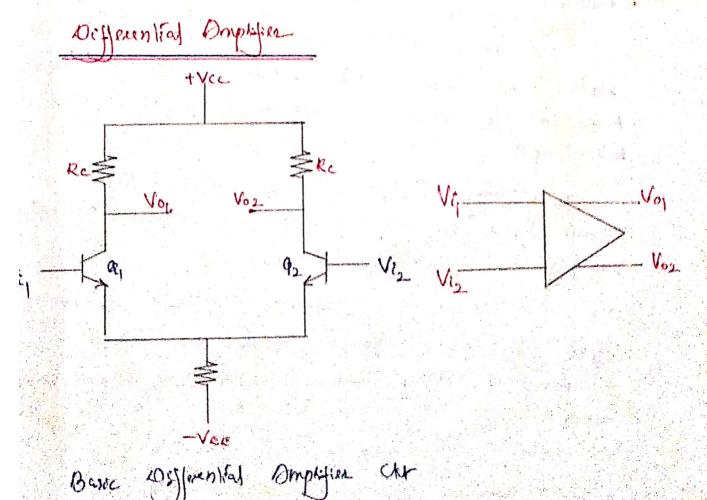

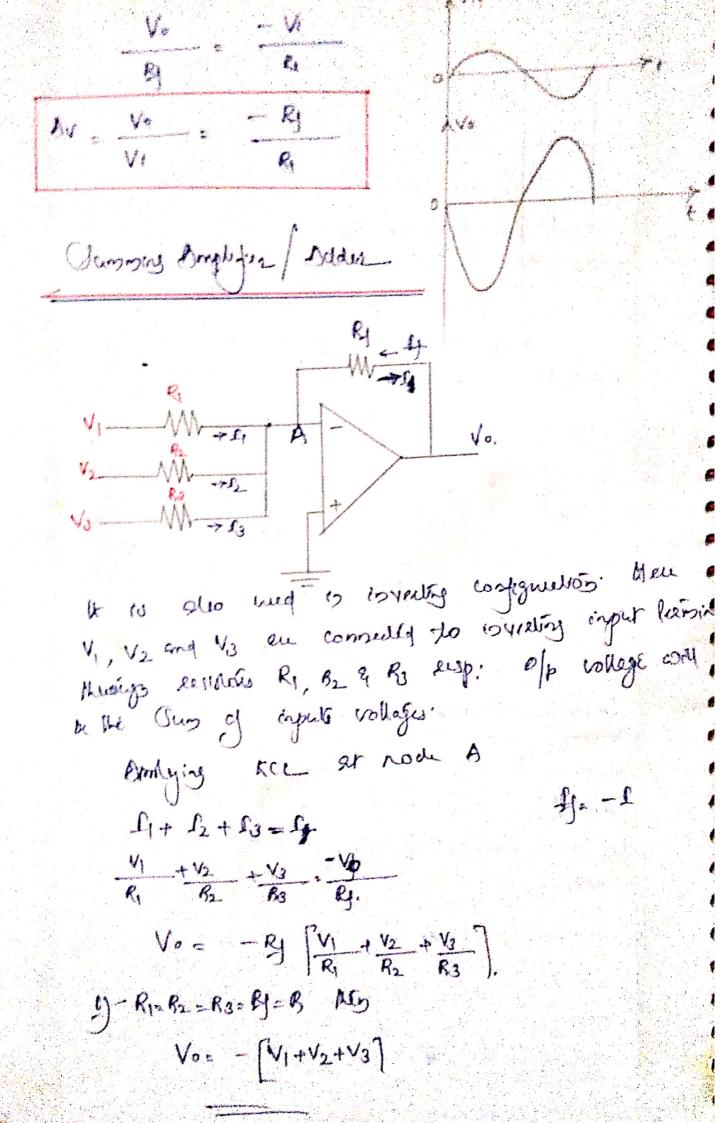

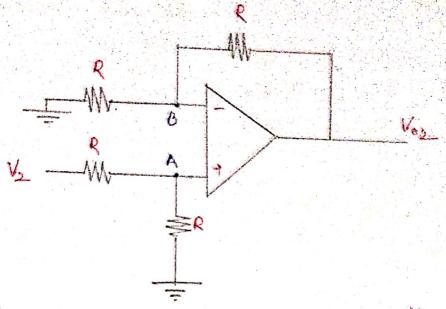

| 5 | Operational amplifiers: Differential amplifier, characteristics of op-amps(gain, bandwidth, slew rate, CMRR, offset voltage, offset current), comparison of ideal and practical op-amp(IC741), applications of op-amps- scale changer, sign changer, adder/summing amplifier, subtractor, integrator, differentiator,  Schmitt trigger, Wien bridge oscillator.                                                                                                                    | 8 | 20 % |

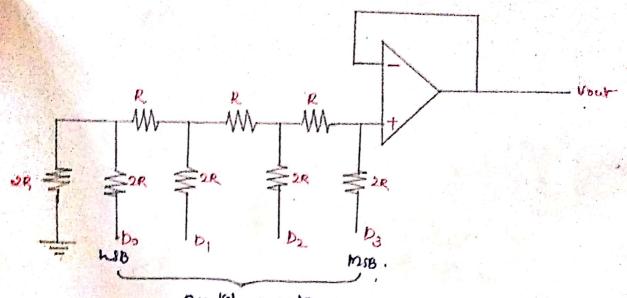

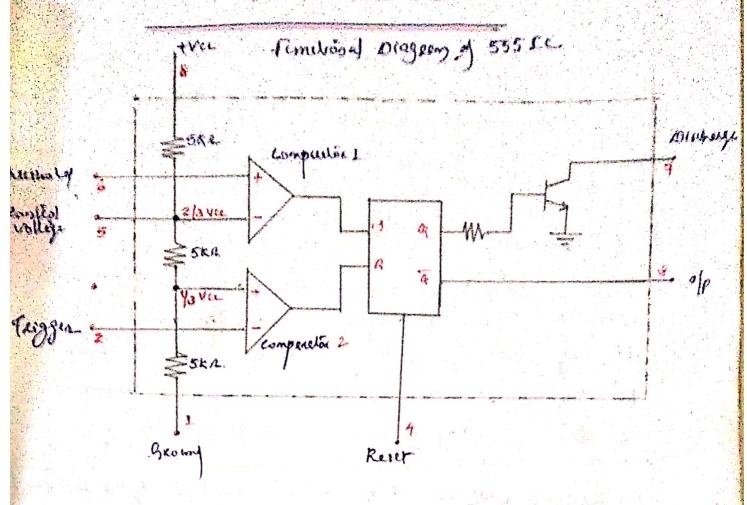

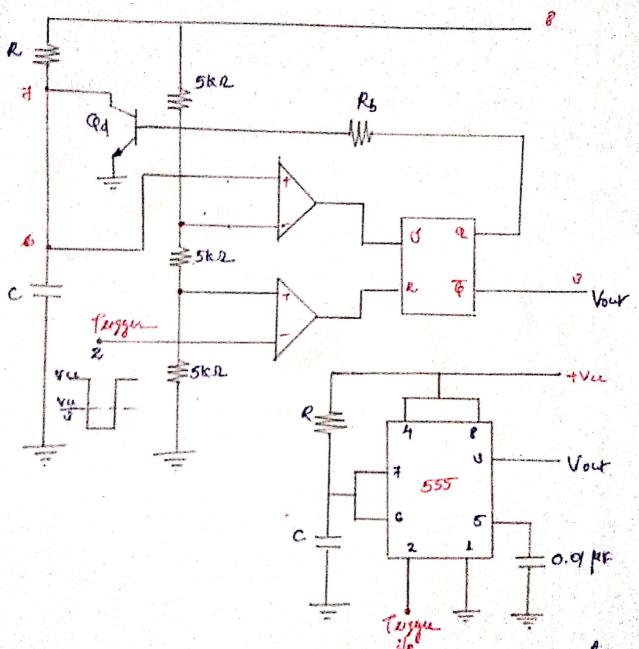

| 6 | Integrated circuits: Active filters – Low pass and high pass (first and second order) active filters using op-amp with gain (No analysis required).  D/A and A/D convertors – important specifications, Sample and hold circuit.  Binary weighted resistor and R-2R ladder type D/A convertors. (concepts only).  Flash, dual slope and successive approximation type A/D convertors.  Circuit diagram and working of Timer IC555, astable and monostablemultivibrators using 555. | 8 | 20 % |

#### Question Paper Pattern:

- 1. There will be five parts in the question paper A, B, C, D, E

- 2. Part A

- a. Total marks: 12

- Four questions each having 3 marks, uniformly covering module I and II; All four questions have to be answered.

- 3. Part B

- a. Total marks: 18

- <u>Three</u> questions each having <u>9</u> marks, uniformly covering module I and II;

<u>Two</u> questions have to be answered. Each question can have a maximum of three subparts

- 4. Part C

- a. Total marks: 12

- Four questions each having 3 marks, uniformly covering module III and IV;

All four questions have to be answered.

- 5. Part D

- a. Total marks: 18

- Three questions each having 9 marks, uniformly covering module III and IV;

Two questions have to be answered. Each question can have a maximum of three subparts

- 6 Part E

- a. Total Marks: 40

- <u>Six</u> questions each carrying 10 marks, uniformly covering modules V and VI; four questions have to be answered.

- c. A question can have a maximum of three sub-parts.

- There should be at least 60% analytical/numerical/design questions.

### **QUESTION BANK**

### **MODULE I**

| Q:NO: | QUESTIONS                                                                                                                        | CO  | KL | PAGE NO: |

|-------|----------------------------------------------------------------------------------------------------------------------------------|-----|----|----------|

| 1     | Describe about <b>non-linear wave shaping.</b>                                                                                   | CO1 | K2 | 1        |

| 2     | Discuss about non-linear network.                                                                                                | CO1 | К3 | 3        |

| 3     | List out the applications of voltage comparator.                                                                                 | CO1 | К3 | 4        |

| 4     | Explain the operation of positive clamper (Negative peak clamper).                                                               | CO1 | K2 | 7        |

| 5     | Explain the operation of negative clamper (positive peak clamper).                                                               | CO1 | K2 | 8        |

| 6     | Explain the working of RC low pass filter, how it can be act as an integrator.                                                   | CO1 | K2 | 3        |

| 7     | Explain the working of RC high pass filter, how it can be act as an differentiator.                                              | CO1 | K2 | 4        |

| 8     | Explain about Sweep circuits? Explain the working of a simple sweep circuit using transistor as a switch with relevant sketches. | C01 | К2 | 12       |

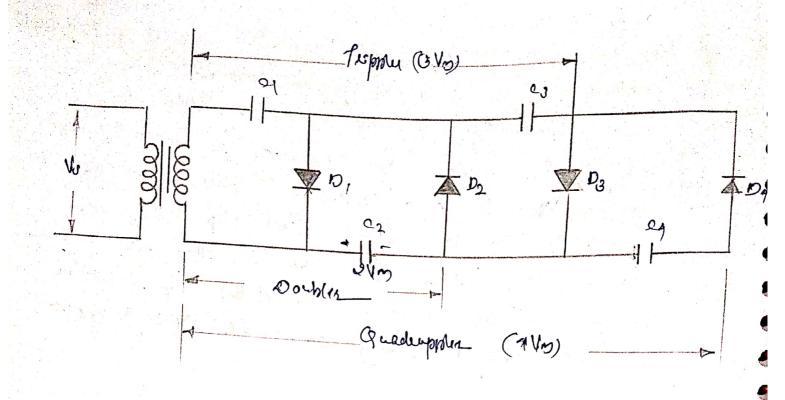

| 9     | Explain the working of Voltage Doubler/Tripler/Quadruppler with help of a neat sketch.                                           | CO1 | K2 | 10       |

| 10    | Explain the working of Clamper Circuits with Diagrams.                                                                           | C01 | K2 | 8        |

| 11    | Explain the working of Clipping Circuits with Diagrams.                                                                          | C01 | K2 | 7        |

|       |                                                                                                                                  |     |    |          |

| MODULE II |                                                                                                                        |     |    |    |  |

|-----------|------------------------------------------------------------------------------------------------------------------------|-----|----|----|--|

| 1         | Expain unregulated power supply is not good ?enough for many applications in electronics?                              | CO2 | K2 | 13 |  |

| 2         | Discuss about series voltage regulators are called Linear voltage regulators?                                          | CO2 | K2 | 22 |  |

| 3         | List out the limitations of series Voltage regulators?                                                                 | CO2 | К3 | 20 |  |

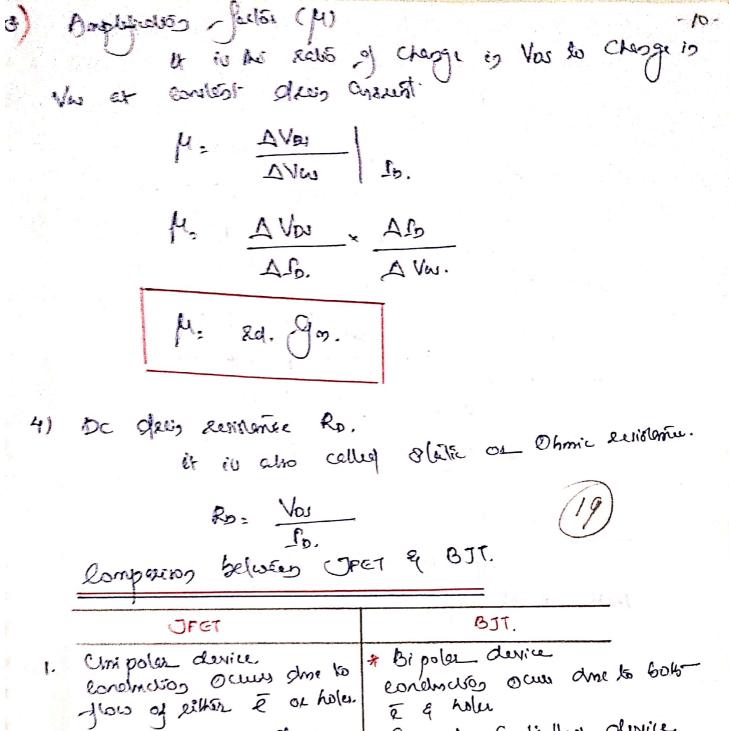

| 4         | Explain why BJT is called bipolar device while FETs are called Unipolar device?                                        | CO2 | K4 | 21 |  |

| 5         | Draw the circuit diagram of Zener-voltage regulator and explain how line & Load regulation is achieved in the circuit. | CO2 | К3 | 12 |  |

| 6         | Explain with diagram the fold back current limiting circuit.                                                           | CO2 | K2 | 25 |  |

| 7         | Explain how short circuit & overload protection is achieved in series voltage regulators.                              | CO2 | K2 | 26 |  |

| 8         | Explain with sketches the working of IC 723 as Low & high Voltage regulator.                                           | CO2 | K2 | 32 |  |

| 9         | Draw the block diagram & Explain 3 terminal voltage regulators.                                                        | CO2 | K4 | 33 |  |

| 10        | Explain with diagram the functioning of SMPS.                                                                          | CO2 | K2 | 35 |  |

| 11        | Define pinch -off voltage of a JFET and explain its significance?                                                      | CO2 | K1 | 32 |  |

| 12        | Draw the Structural diagram of MOSFET and explain its operation.                                                       | CO2 | K2 | 36 |  |

| 13        | Draw the Structural diagram of N- Channel JFET and explain its operation.                                              | CO2 | K2 | 37 |  |

|           | MODULE III                                                                                                             |     |    |    |  |

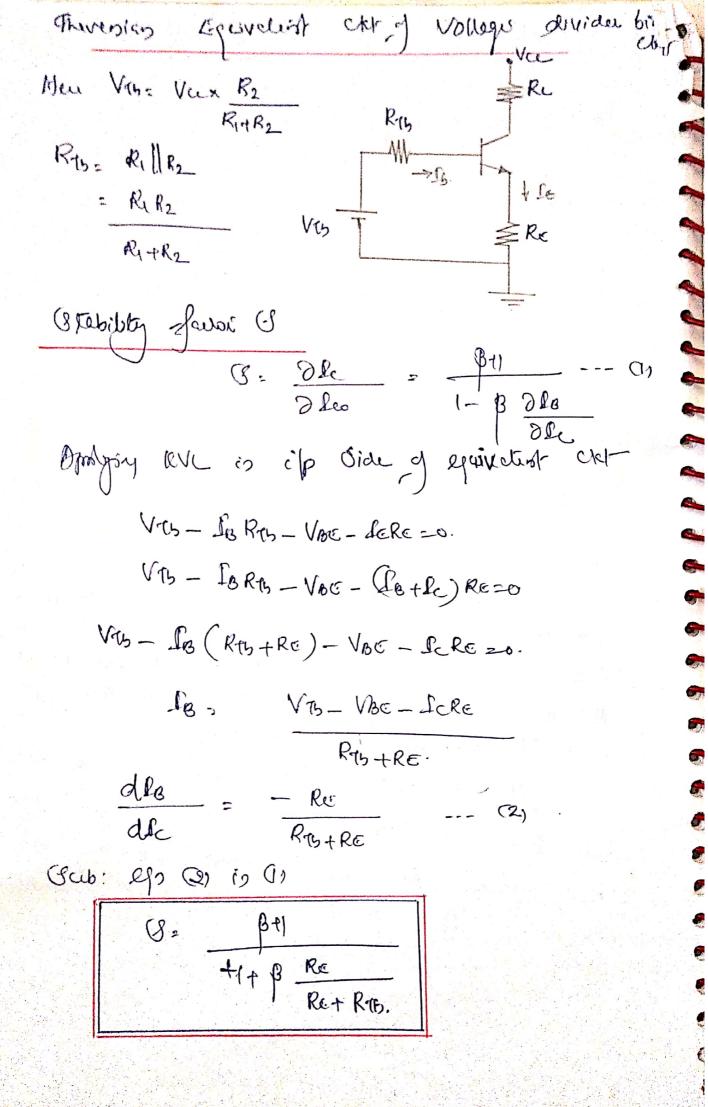

| 1         | Define Stability factor & derive the general expression for stability factor.                                          | C03 | K1 | 53 |  |

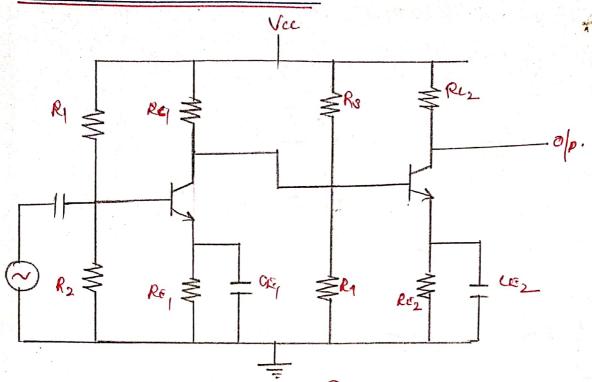

| 2         | Discuss about multistage amplifier circuit?                                                                            | CO3 | К3 | 62 |  |

| 3         | Explain about cascaded amplifiers? Explain the                                                                         | CO3 | K2 | 63 |  |

|    | effect of cascading on Gain & Bandwidth.                                                                  |     |    |    |

|----|-----------------------------------------------------------------------------------------------------------|-----|----|----|

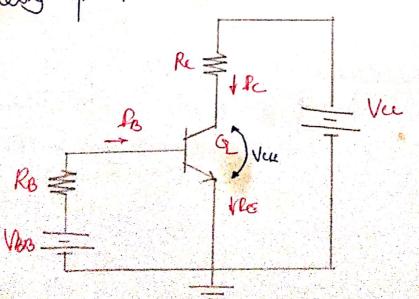

| 4  | Draw fixed Biased circuit & derive its Stability factor.                                                  | CO3 | К3 | 54 |

| 5  | Expain about voltage divider bias circuit.Derive the expression for stability factor                      | CO3 | K4 | 55 |

| 6  | Expain about dc load and ac load line                                                                     | CO3 | K2 | 56 |

| 7  | Expalin detail about multistage amplifiers                                                                | CO3 | K2 | 67 |

| 8  | Draw the neat diagram of common source amplifier with neat diagram                                        | CO3 | К3 | 67 |

| 9  | Expain about effect of negative feed back on amplifier                                                    | CO3 | K2 | 68 |

| 10 | Draw the circuit dagram of direct coupled amplifier,Explain its working                                   | CO3 | К3 | 69 |

|    | MODULE IV                                                                                                 |     |    |    |

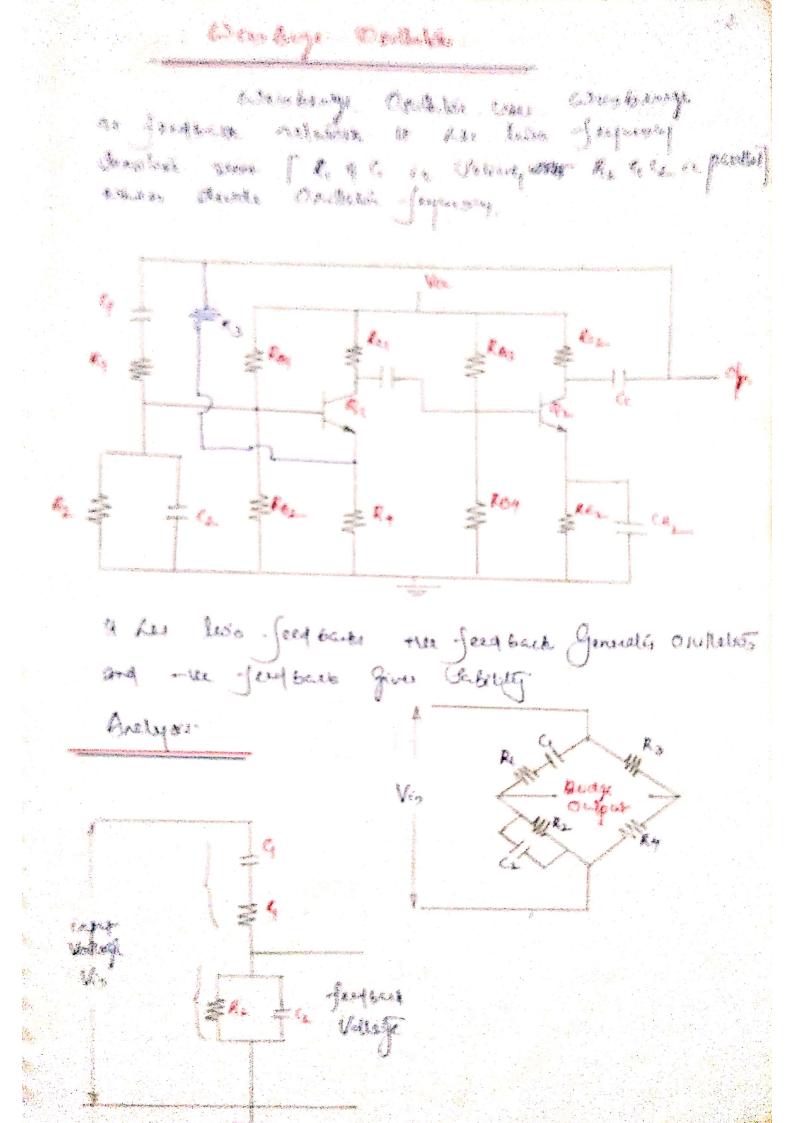

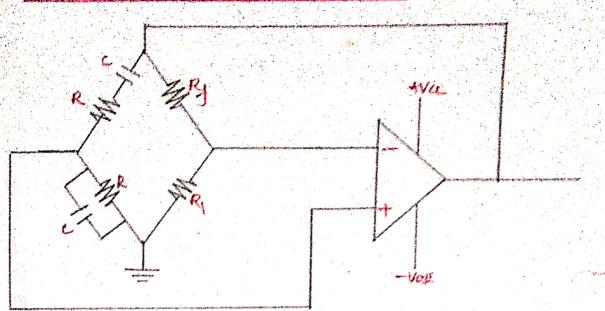

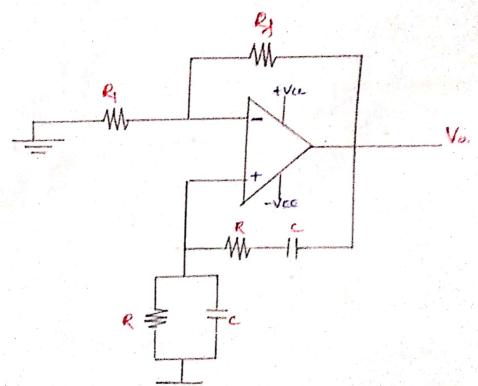

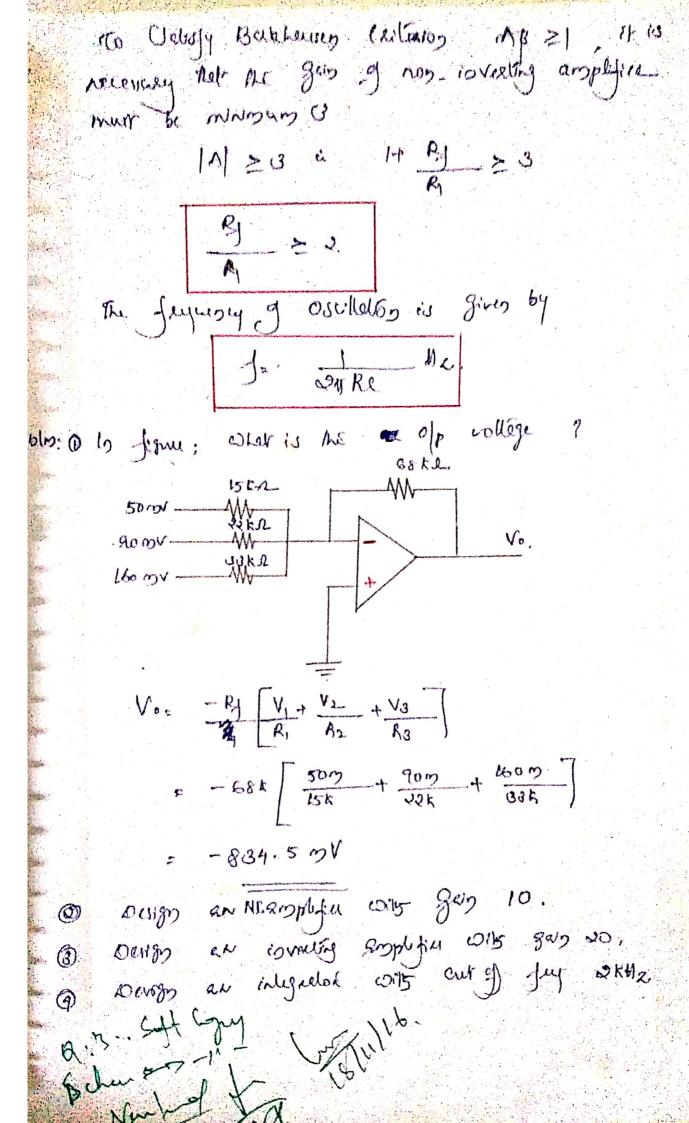

| 1  | Draw the circuit & explain the working of Wein bridge oscillator. Also derive its frequency of operation. | CO4 | К3 | 78 |

| 2  | Explain the concept involved in crystal oscillator with its characteristics?                              | CO4 | К2 | 78 |

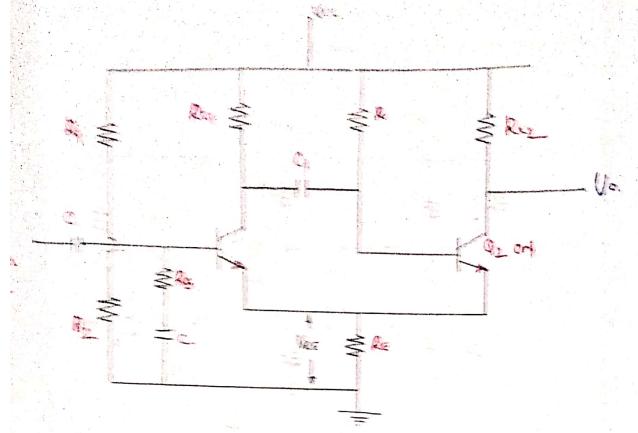

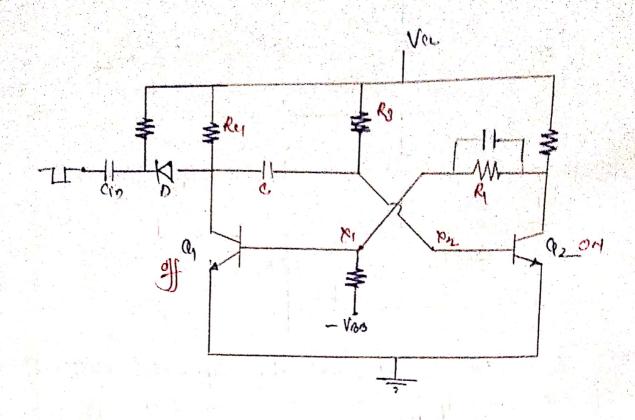

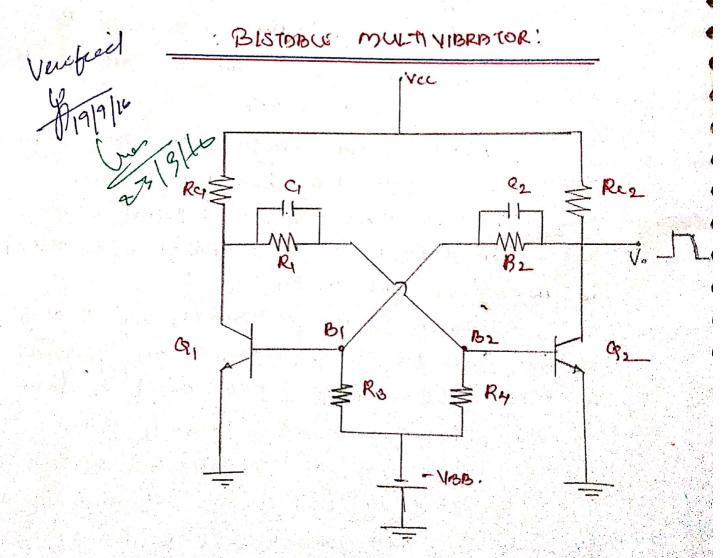

| 3  | Explain Bistable Multivibrator                                                                            | CO4 | K2 | 85 |

| 4  | Explain about collector coupled Astable Multivibrator                                                     | CO4 | K2 | 86 |

| 5  | Explain emitter coupled Astable Multivibrator                                                             | CO4 | K2 | 87 |

| 6  | Draw and explain a one-shot circuit.                                                                      | CO4 | K2 | 86 |

| 7  | Discuss the conditions for sustained oscillator or what is Barkhausen criterion?                          | CO4 | К3 | 77 |

| 8  | List out the classifications of Oscillators?                                                              | CO4 | К3 | 76 |

| 9  | Explain types of feedback oscillators?                                                   | CO4 | K2 | 77  |

|----|------------------------------------------------------------------------------------------|-----|----|-----|

| 10 | List the conditions for oscillation?                                                     | CO4 | K2 | 78  |

| 11 | Define Piezoelectric effect.                                                             | CO4 | K1 | 85  |

| 12 | Explain Miller crystal oscillator? Explain its operation.                                | CO4 | K2 | 86  |

|    | MODULE V                                                                                 |     |    |     |

| 1  | Compare ideal and practical Op-Amp parameters                                            | CO5 | К3 | 94  |

| 2  | Explain Slew Rate & what causes slew rate.                                               | CO5 | K2 | 95  |

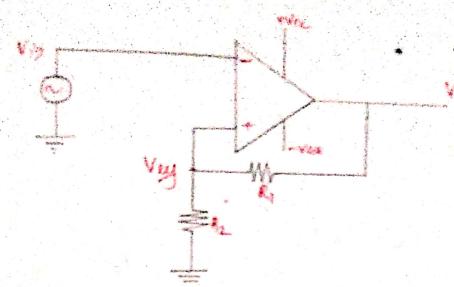

| 3  | Explain the application Op-Amp as Sign<br>Changer & Scale Changer.                       | CO5 | К3 | 96  |

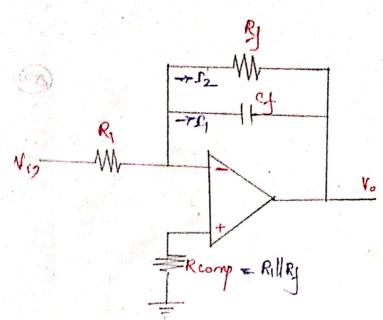

| 4  | Write Notes on Integrator & Differentiator using Op-Amp.                                 | CO5 | К3 | 97  |

| 5  | Explain the application Op-Amp as Summing & Difference Amplifier                         | CO5 | K2 | 98  |

| 6  | Draw and explain Schmitt trigger Using Opamp                                             | CO5 | К3 | 104 |

| 7  | Draw the circuit diagram of Wien bridge oscillator Using Op amp & Explain its operation. | CO5 | К3 | 108 |

|    | MODULE VI                                                                                |     |    |     |

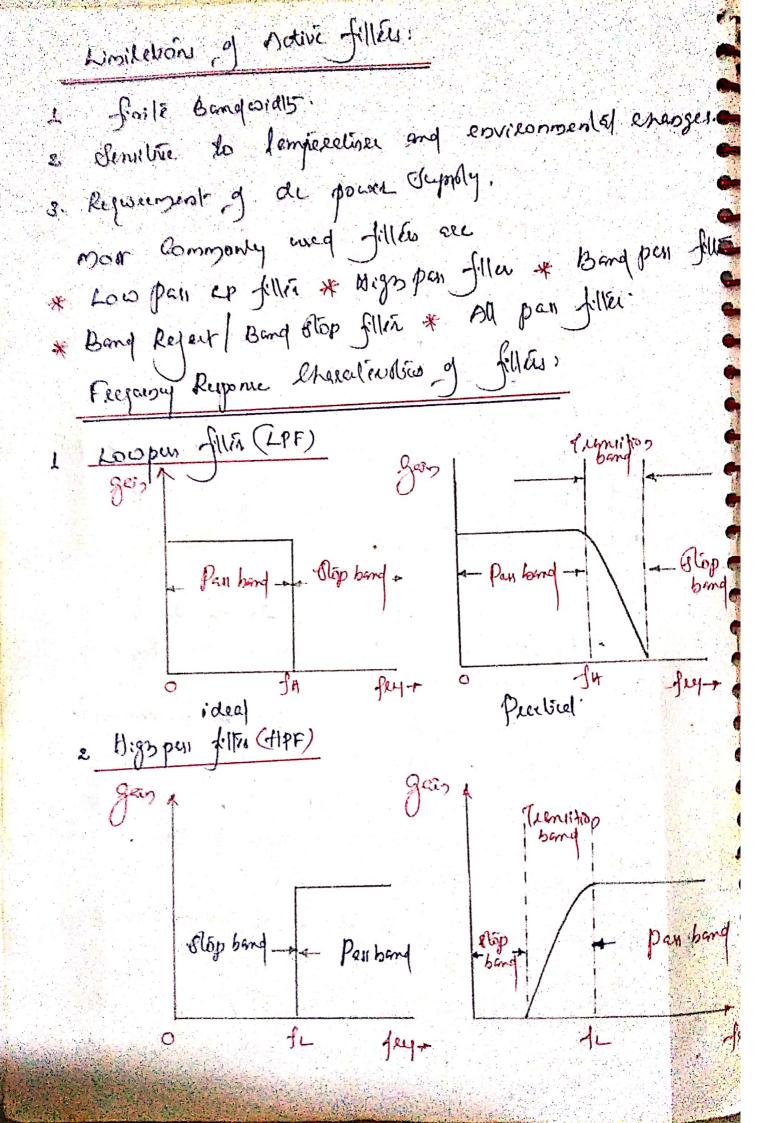

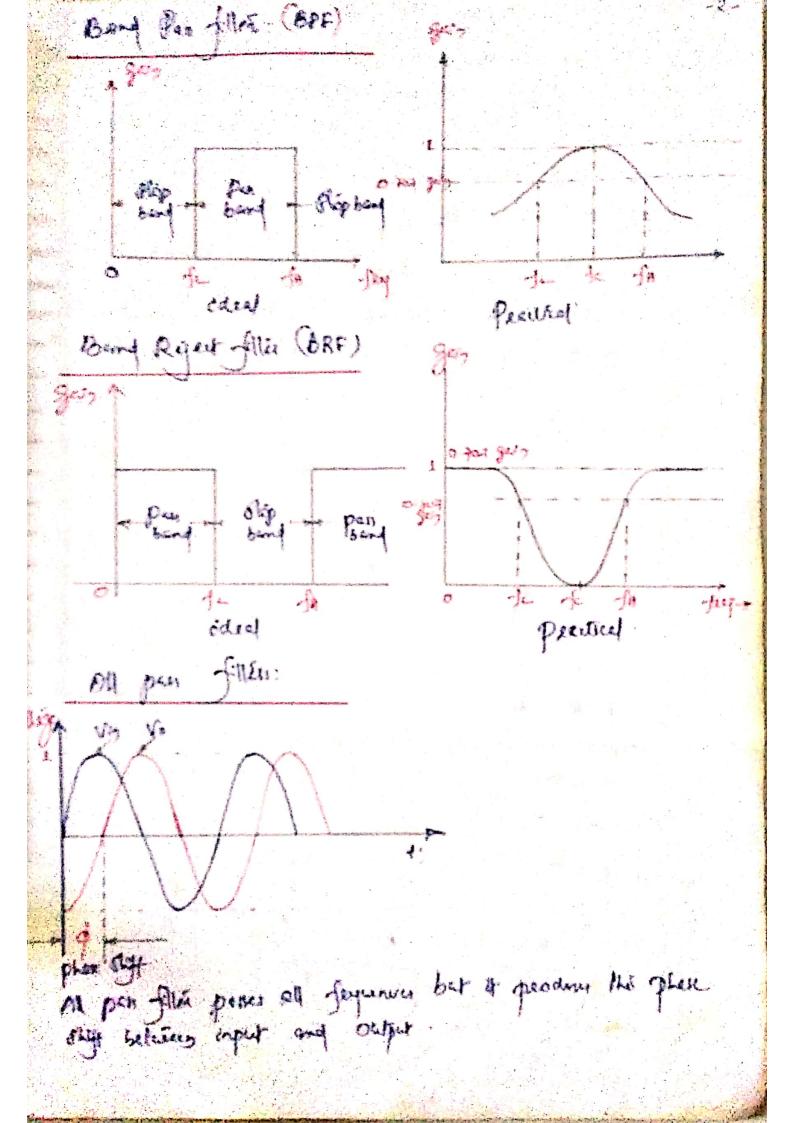

| 1  | List-out the Advantages & Disadvantages of<br>Active filters over Passive filters.       | C06 | К3 | 110 |

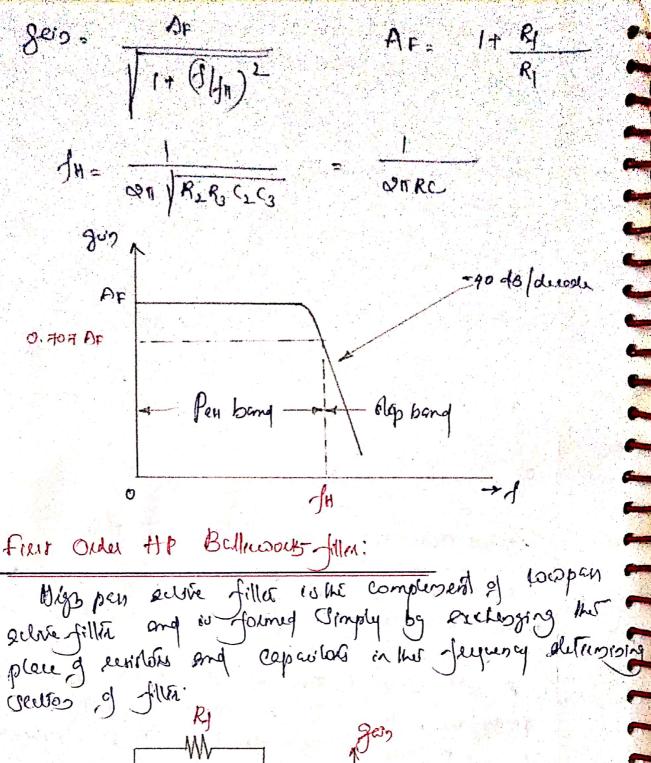

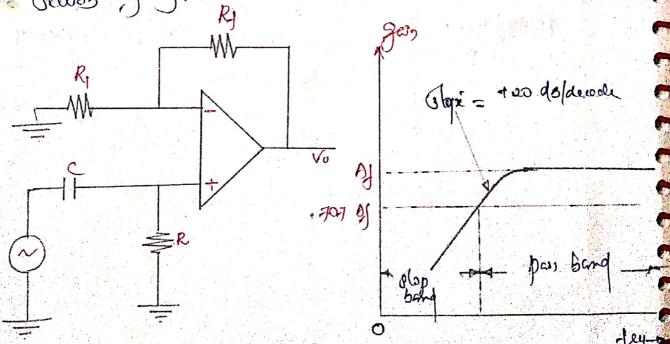

| 2  | Explain about Butterworth filters? Explain its Ist order LP & HP filters.                | C06 | K2 | 111 |

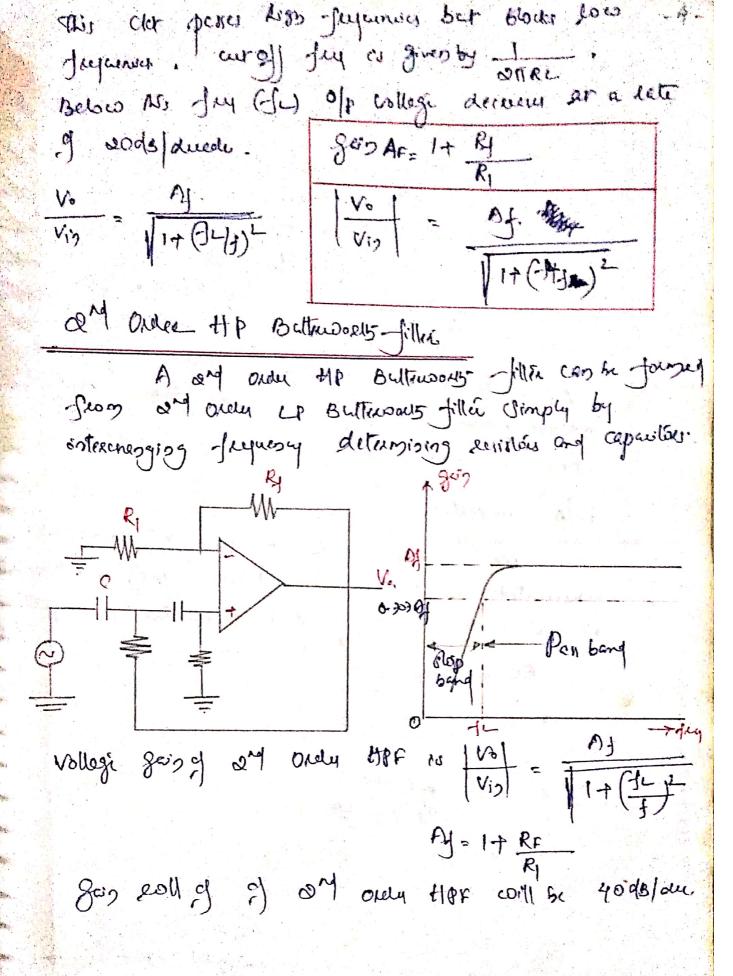

| 3  | Draw and explain 2nd order Butterworth LPF<br>& HPF                                      | CO6 | K2 | 114 |

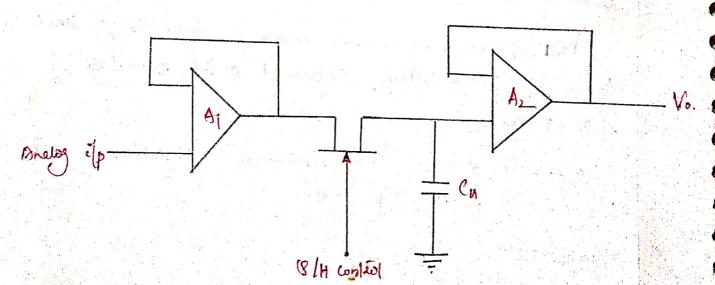

| 4  | Explain with a diagram the principle of working of Sample & Hold Circuit.                | CO6 | K2 | 115 |

| 5  | List out the specifications of Digital to Analog<br>Converters                           | C06 | К3 | 118 |

| 6  | Explain the working of Dual slope ADC with the    | CO6 | K2 | 120 |

|----|---------------------------------------------------|-----|----|-----|

|    | help of a Diagram                                 |     |    |     |

| 7  | Explain the working of SAR & Flash type ADCs      | CO6 | K2 | 121 |

|    | with the help of a Diagram                        |     |    |     |

| 9  | Draw the Functional block Diagram of 555          | CO6 | К3 | 129 |

|    | Timer IC and Explain its operation as Astable-    |     |    |     |

|    | Multi vibrator.                                   |     |    |     |

| 10 | Draw the Diagram of Monostable Multi-             | CO6 | КЗ | 130 |

|    | vibrator using 555 IC and explain its operation   |     |    |     |

| 11 | Design a Butterworth LPF having Cutoff            | CO6 | K5 | 132 |

|    | frequency of 2 KHz and pass band gain of 2.5      |     |    |     |

| 12 | Design a second order LPF at cutoff frequency     | CO6 | K5 | 134 |

|    | 1KHz                                              |     |    |     |

| 13 | Determine the resolution of                       | CO6 | K5 | 134 |

|    | a). 6 Bit DAC                                     |     |    |     |

|    | b). 12 Bit DAC in terms of percentage             |     |    |     |

| 14 | Design a 4 bit weighted Resistor DAC whose        | CO6 | K5 | 135 |

|    | full scale output voltage is -5V.logic levels are |     |    |     |

|    | 1= +5V; 0= -5V.What is the output voltage         |     |    |     |

|    | when input voltage is 1101                        |     |    |     |

| 15 | An 8 bit DAC produce Vout = 0.05V for a Digital   | CO6 | K5 | 135 |

|    | input of 00000001.Find full scale output. What    |     |    |     |

|    | is its resolution. What is output for an input of |     |    |     |

|    | 00101010                                          |     |    |     |

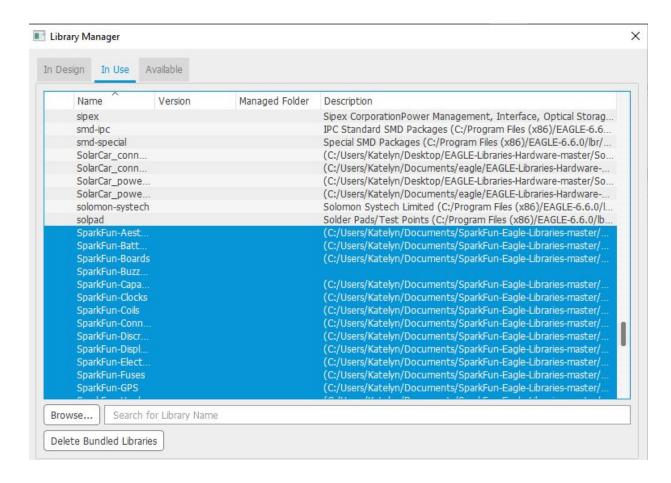

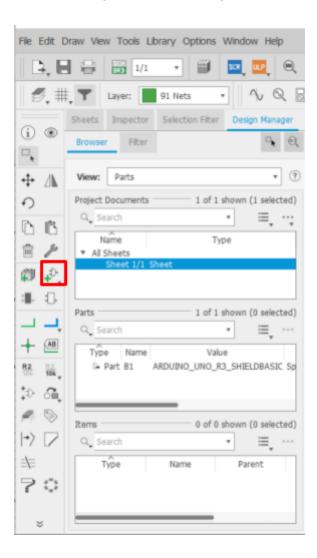

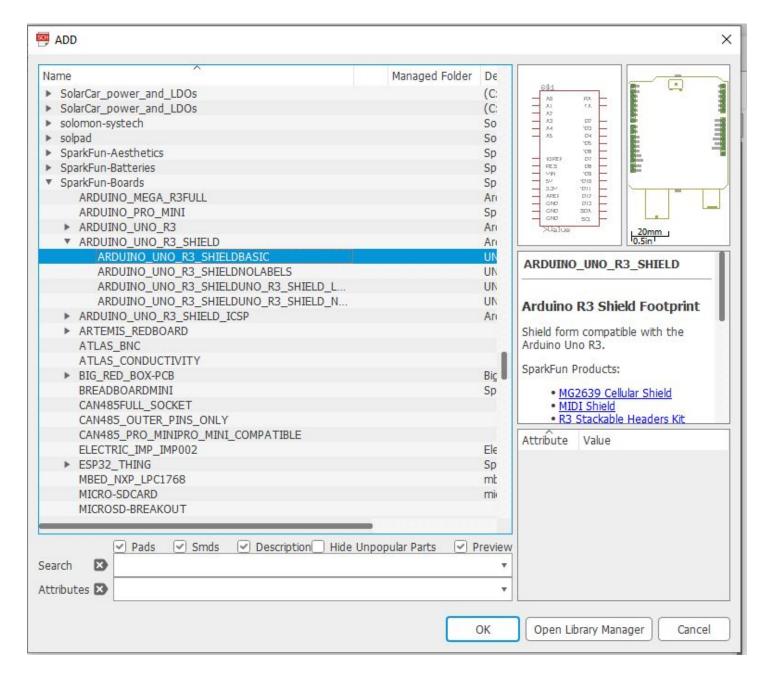

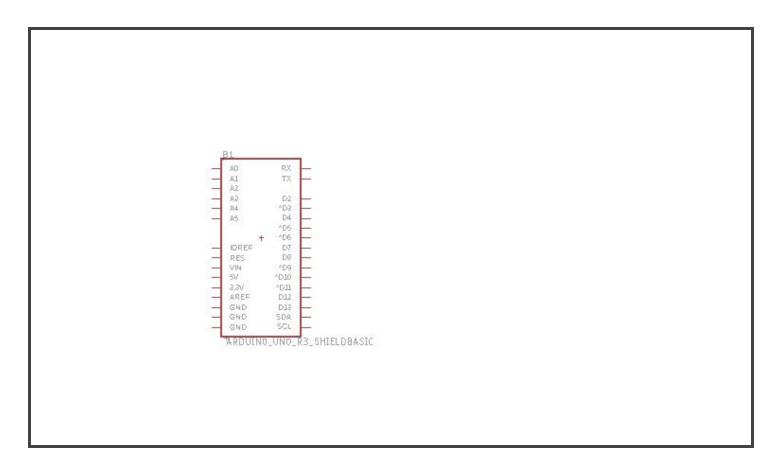

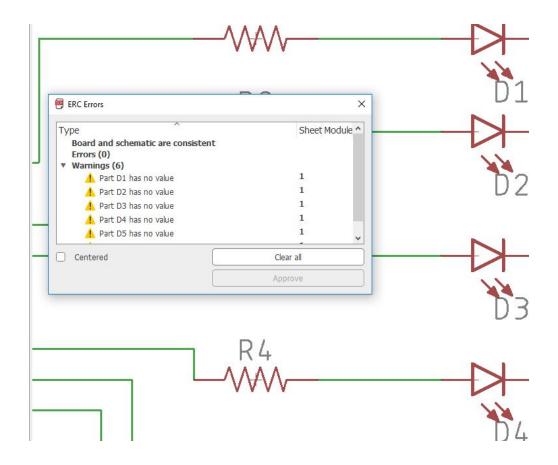

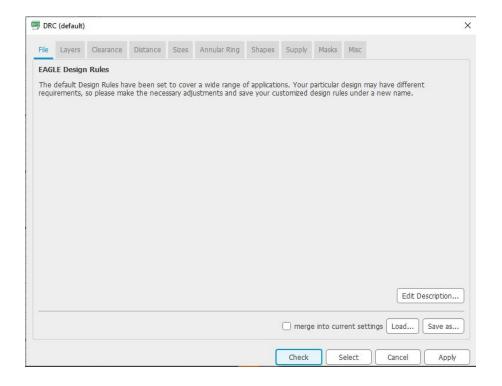

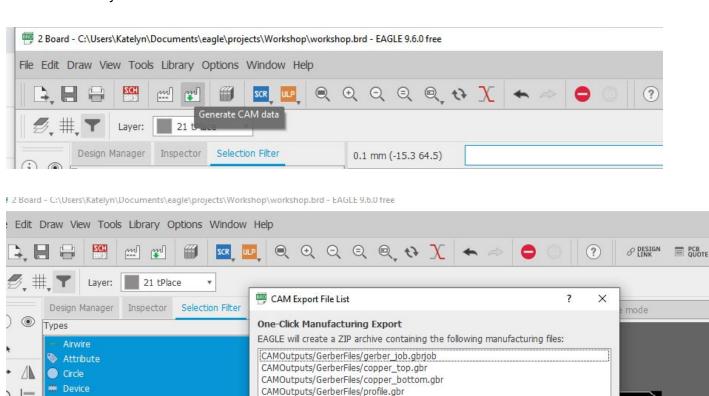

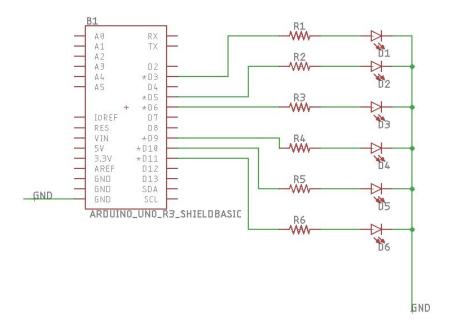

| APPENDIX 1                  |          |

|-----------------------------|----------|

| CONTENT BEYOND THE SYLLABUS |          |

| TOPIC                       | PAGE NO: |

.

S:NO;

1

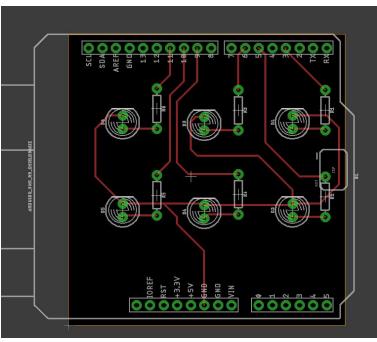

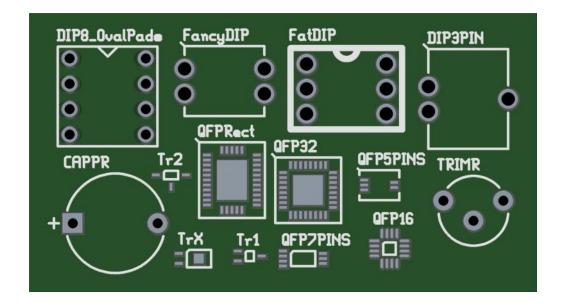

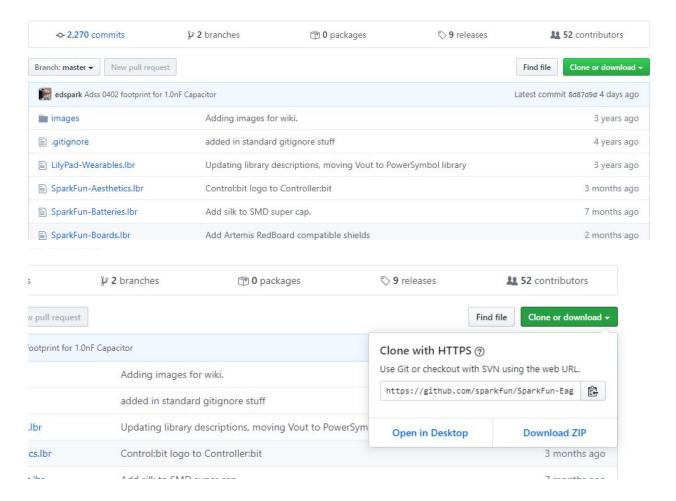

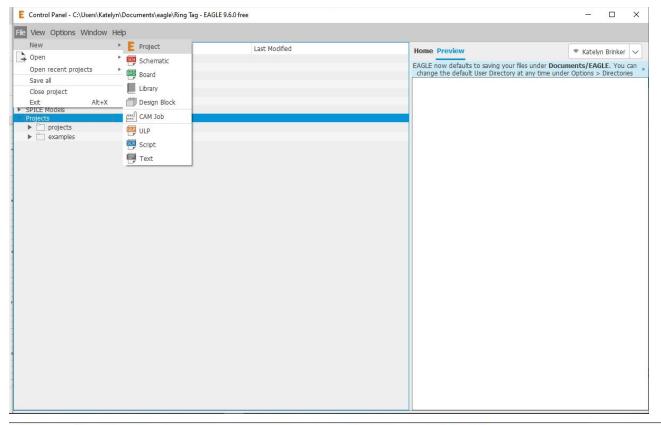

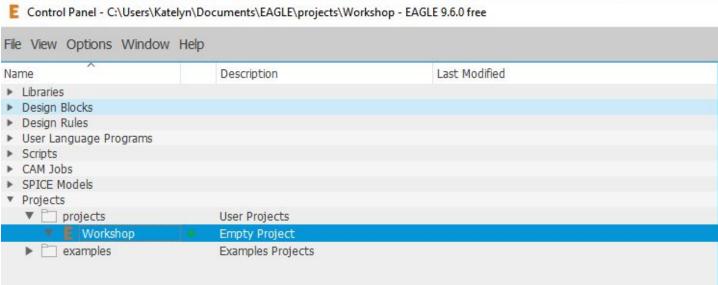

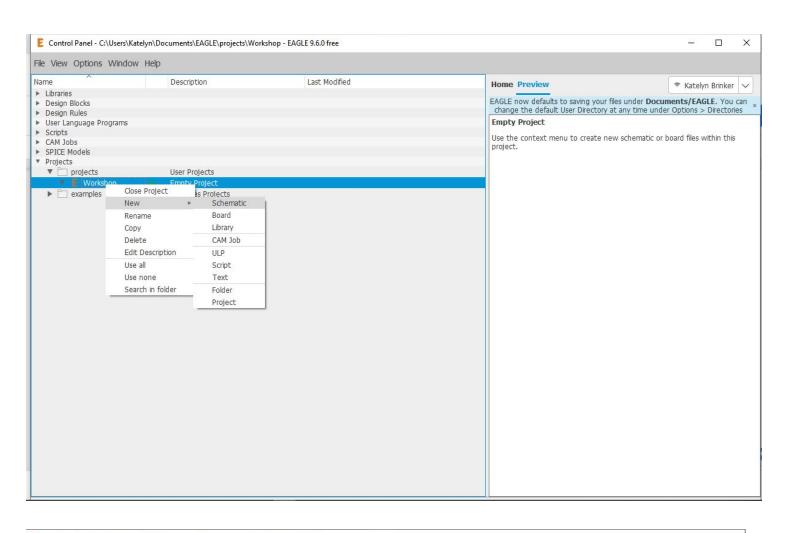

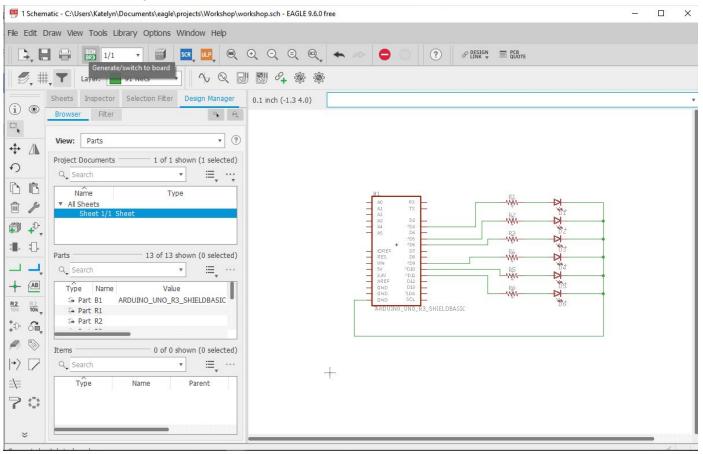

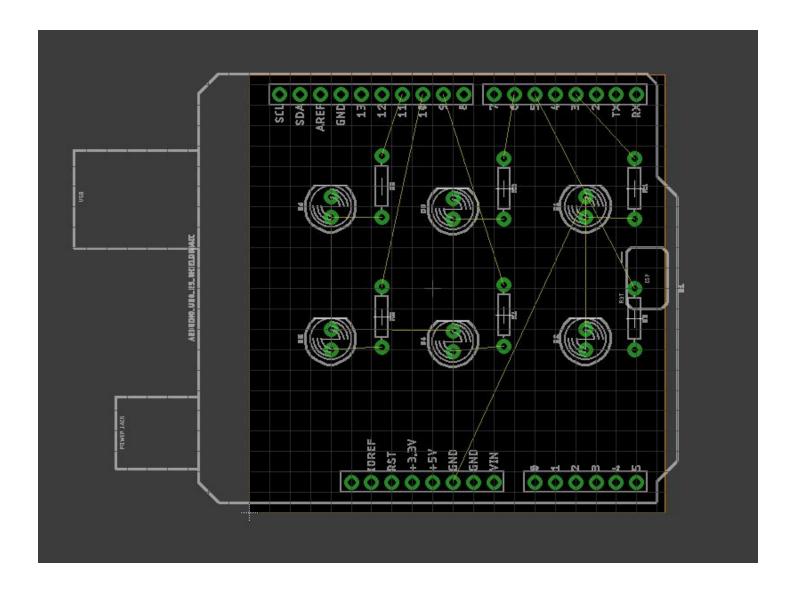

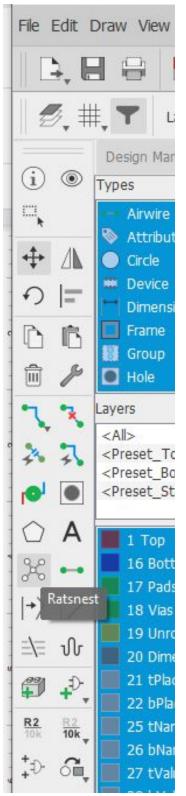

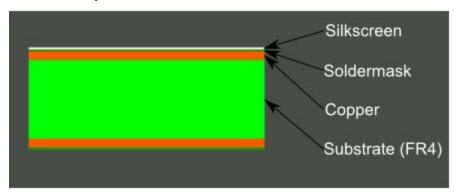

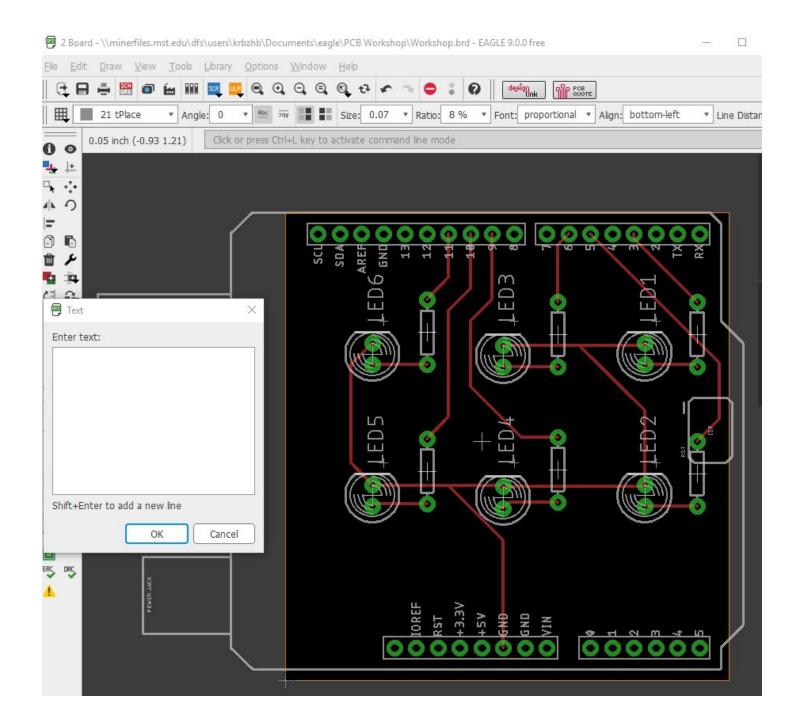

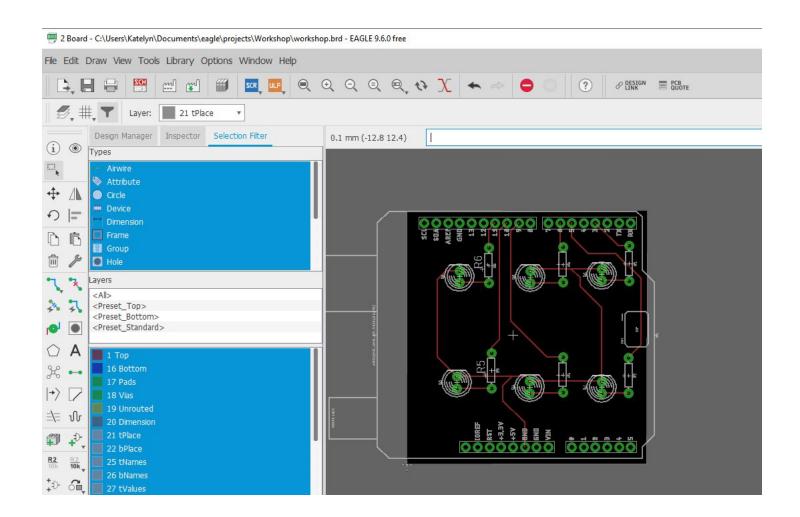

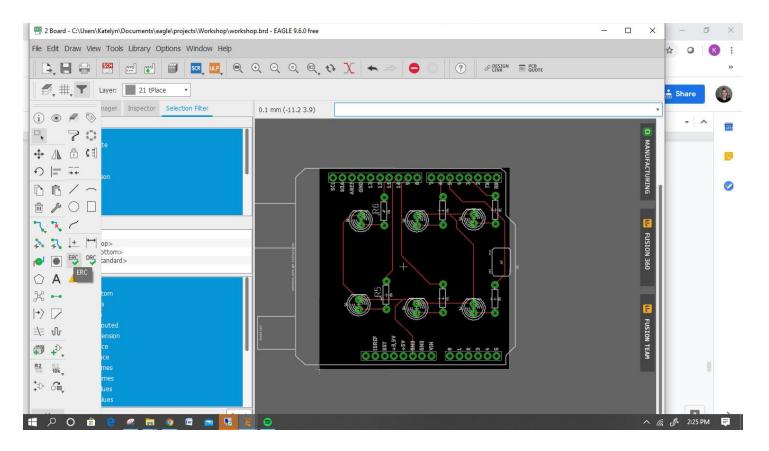

PCB DESIGN

139

# : WAVE SHAPING CIRCUITS:

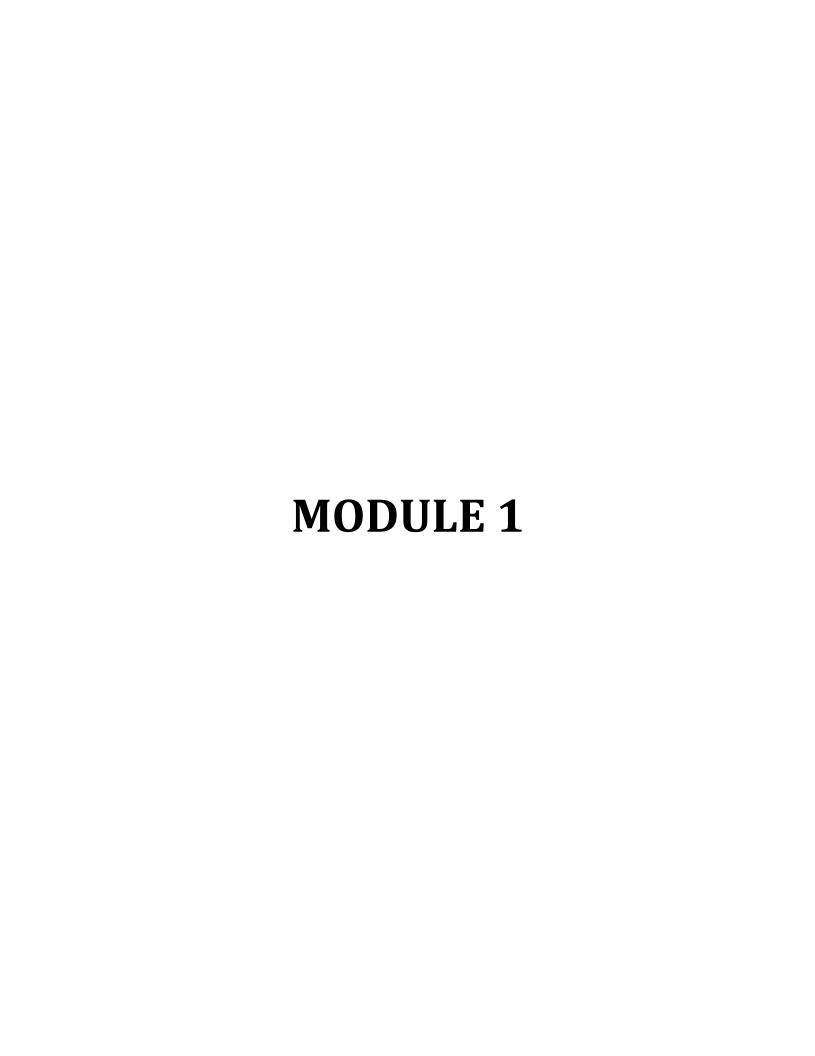

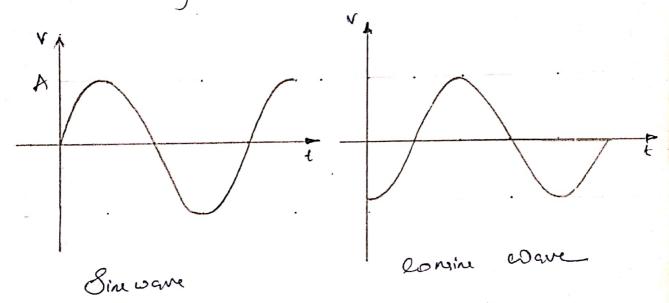

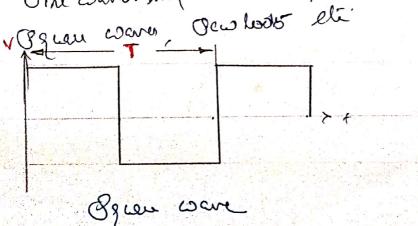

Pinnoidel & Non. Sinnoidel Dave Braper:

A d'in coave on d'invaid és à mallimaticel luve their densities à moots repetative describes à l'une as the independent des l'a d'invaided. It variable. A comme wave ou a d'invaided. It variable. A comme wave ou a d'invaided by 90°. Les the same form best it has been pleu Phillip by 90°.

yas= A Piner

A = Angelende es = Angeler Jupeney.

A non Sinusial Waveform in on that is not a Oin wave. and on Enamphs see Evangular, but anywher

T 2 10 20

# Ochfenslide & Wagneting Christ:

# Offerwhiting Creat:

A Cirwit in which of vollage is directly proportional to the derivative of input is known es differentiating Crawit.

A differentiating chr is a simple le coust esteu mi op is teres acconstité residér R. estate la de or consert input is apprised à seux a chr. Mi op will be zon.

hordre to retieve good dessentation the following line Conditions Chowled be Vehrefied.

- 1. The Time Constable RC of the should be much small should be much so small single source in on more limit

- 2 The volue of Xc showly be 10 or now him.

Geodei Mass R of operating Supersy. Xc > LOR.

Fulfilled has conditions the op quality of supers.

dervolver of his input college of it is is consession

a capacitan co dy = 9 (2) = 9 CVe Bine capartirei Reldonce is much legerthes Ri è/o vollege construor consideres equal la copasibr Ve = Vi e d Vin RC allin Vo= iR when ip is Oguse were when yo jed in aque wave of consist of sharp ranco pula. Daving o'c part of input wave amplifiede charges aboutly and him differentiated of will be charp pale drains const part de épart de sont du zero. was Elp is Enonquer were:

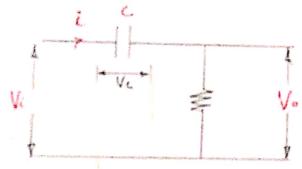

RC integrator Ciruit:

peoportroiel la inlegiel of input in knows es an inlegieling ciruit

i Ru (input)

i W

VR

Vi

VR

In Grow to ochive good integrations

1. The limi contr. RC Browth be very leag company

to lime period of input wave

2. The volume of RI Should be to on more limits  $R \ge 10 \times c$ .

Bine R>> 8c VR: Ve

$\frac{V_R}{R} = \frac{V_c}{R}$ change 8 00 Capacilor 8: \id-8/p Vollage Vo= 2 = = Vo of Tride When ilp is Ognen wave: when input led in Oquer ware, ofp will be luanques wave. On integration meens Cammation; .: 0/p ware form will be sum of input warren or any instant This Ulam in Rees our to and goes on ineversing tell et becomes meximum et c. D'I'll this Gammaliss goes on deereling to the onser of -ve movement cb of input.

The second second A Transfer distributions. Large M. Little No demokel were There into another 1. (5年) Y 11. (625.5) Interestin tempeda com (almerkin Coulogs come DUMAN STILL BOOK

A were Sheping Crewb which contable the shape of op wan form by emony on clipping a poulos ed aprilied wave is known a clipping acount. Hay wave entre is an aramph for dippin

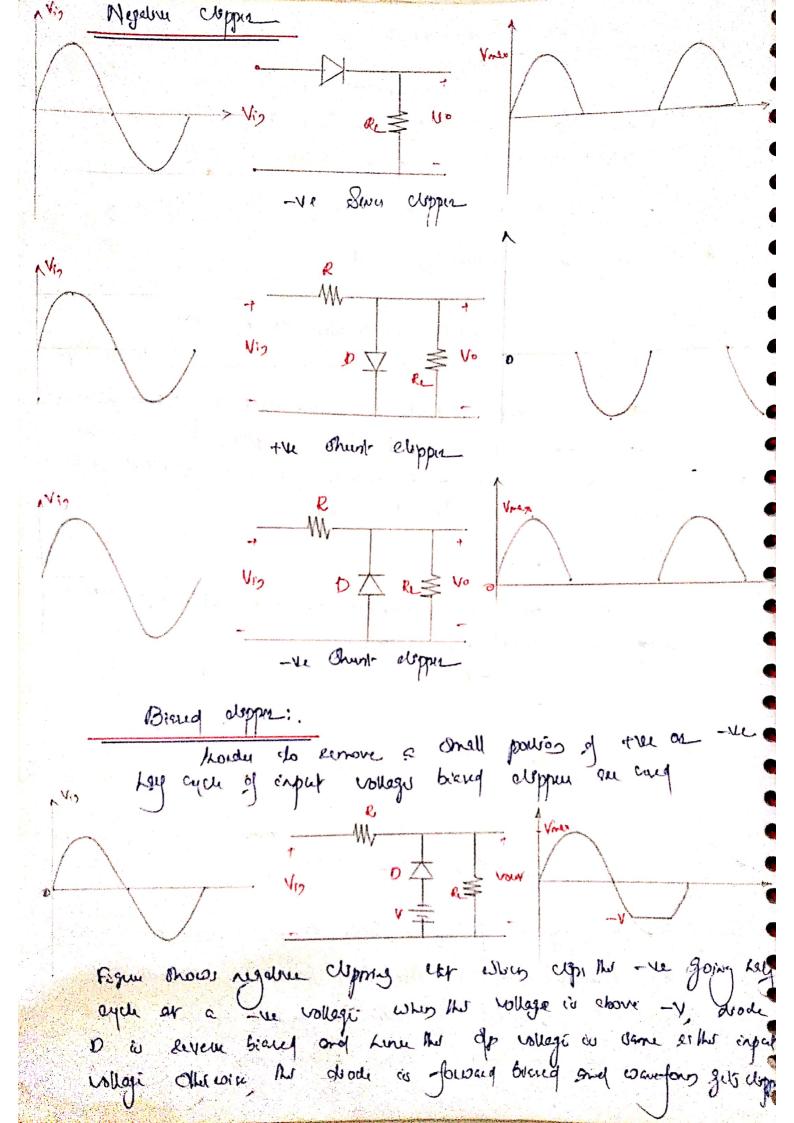

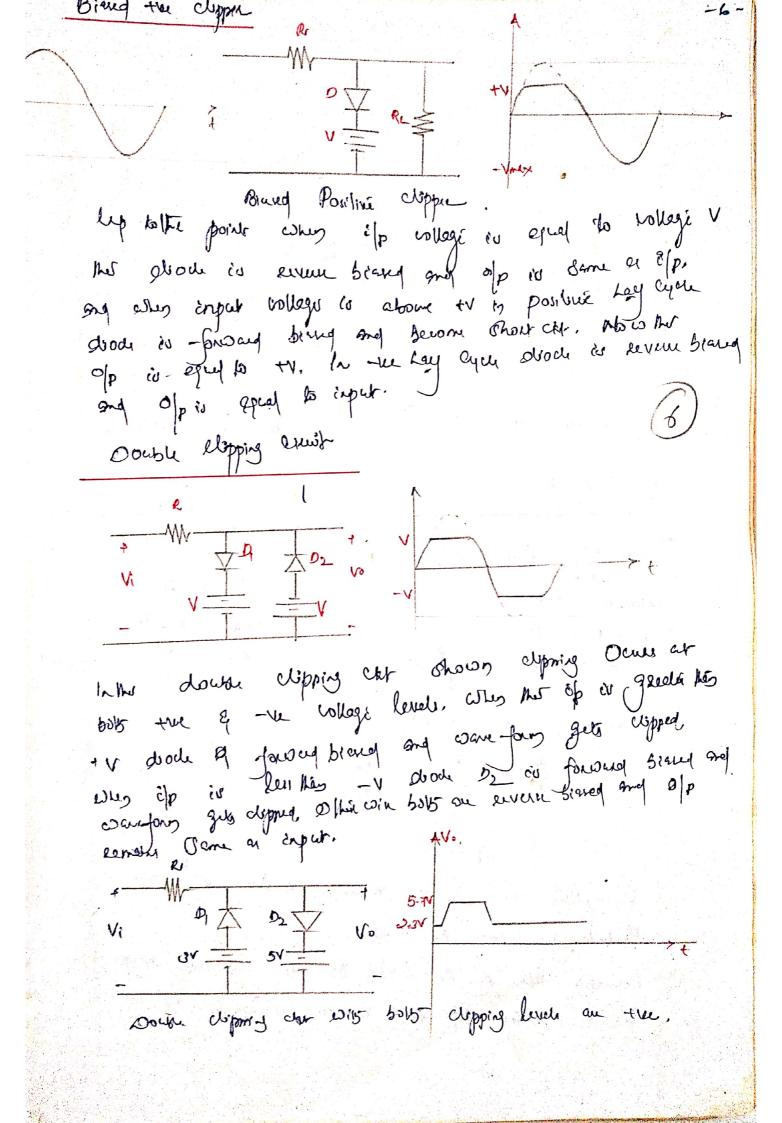

\* According to logignetos ched:

- Sevy Abode elipper

- Shunt or parallel avode dippur

- Combinessés. of diode, Resistance & pour Peoples.

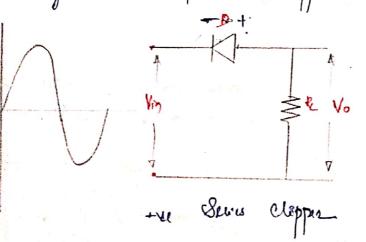

Kep point: When a doch is connected in Sever DIE that load Oach Chr is called Sever clapper. a who that glode às connelled ou à brench assert às parelled to the load it is called Perally elepter.

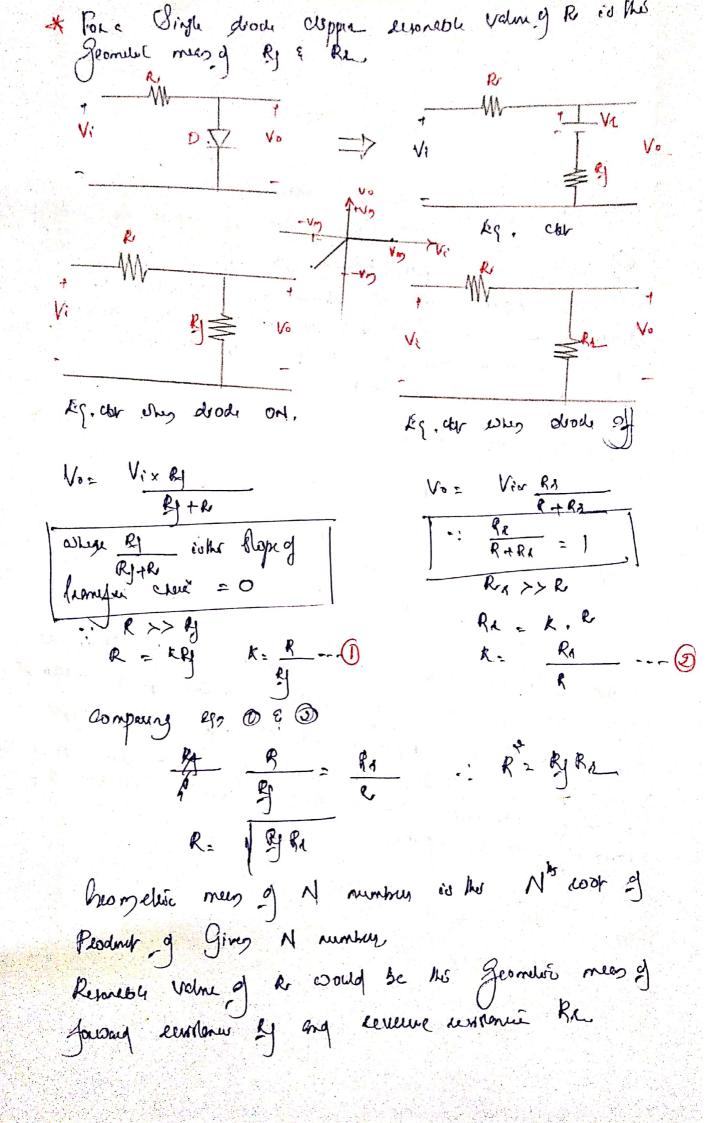

# Positive Coppus:

JJJJJJJJ

A cripper which removes that the hard cycle of input vollages in called the clippon:

alles the colp is possive about I is Revent brand and of lemon keto, a the hay lyon in disprey of Owing - re herjeyer of orgest goods in forward brand and we have even appear amon of.

-

9

3

-

-

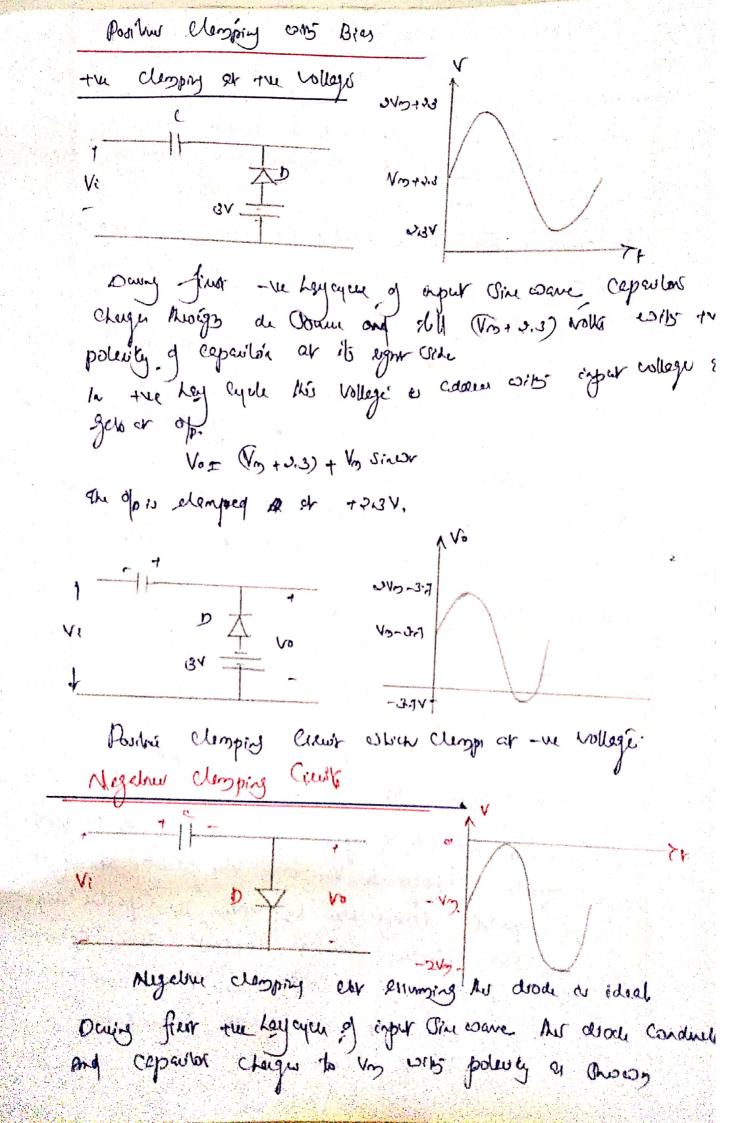

The champing Meliosis is one the will champe of the champing the level, the newson must bet have a capably to introduce it can also employ an independent of Capaply to introduce it can also employ an independent of Capaply to introduce it can also employ an independent of Capaply to introduce it can also entered of the can adoptional obificial obificial obificial obificial obifical obificial o

to it enterposed better the general such that told vollage Ground of the series of the point such that the series of the series

David - Le Ley Cycle of Engar Ginz wave diode Conduction of Coparlin Charge to Vm 2015 the polarity of light and coparlin Charge the Ley cycle the Caparlin Commit Order of coparling discharge Gine about downer conduct. Then Caparling also are all tower of Vm volls Commuted in Gairy 2016 and or a Gairy 2016 are of a Comme of Vm volls commeted in Gairy 2016 and Them The Off vollage caste Deputing of Von Vort Vm Janor

vollage multiples is a court that procume a de vollège agres les on more peab delerpre or serifier. Rollede, wallibrer Jound, abustrappen en the ohm Ligh vollage with low Charant ex Reguled Over as piction tube to Recover Osvillations

A vollage multiplee en an electrical est that convention AC electived power from a lower Vollage la a hogher oc vollege by mening capculate and abodes combined ento a Milwado.

Depending on Ofp Hollage Mulliphen can be

\* Vollege Teipphere

Vollage Gradenpler.

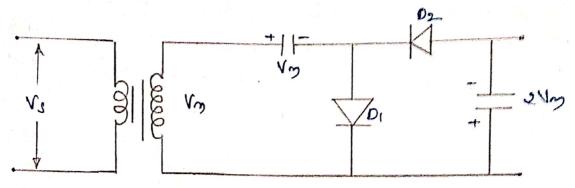

# : VOLTAGE DOUBLERS:

A vollège doubles produces à de vollège almost livice su sem value of input ac vollage.

Vollage doubles can be of two hypes Vollege => Hay wave Kollegi Doubler\_ => Full wave vollage doubles.

# Hay wave vollege boublest:

Figure Onows ekt for HW vollagi double duing the Lay Cycle of 20 vollage, D, conducts and DI is cut off Now capaciton of changes to pieto earlyed vollage Um, with polanty shows in figure During - ve hell after copacited 2° vollege: comes in Steven with volleger person copacited of Thus le will fry to cheese le winds =2 ym Black drode D2 acts as Bhost droving - ve help cy cor ces ces dum the collegis ground the our side to op.

H.W Vollege Boubler

In figur cepauloi G will dunhaige drung - le Lopi cycle Agars 10 the Loy cycle, it blacks chaqing. Thus his Hw vollage doubles Baproley his vollage to the Local in one helf cycles.

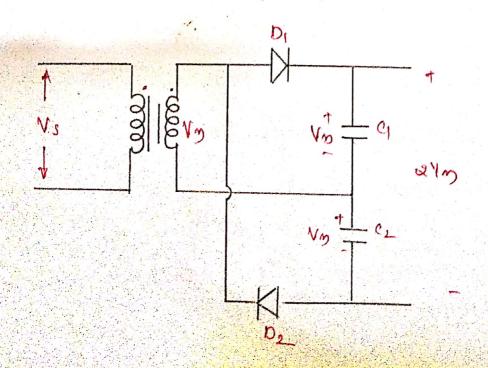

Full wave Vollagi Doubles

Figur Phows FW Vollege Regulation. During -11

Mi the help Cycle of 1º vollege docke Di Conduction Cherging C1 to peak vollege Vn. At this time D2 conduction of non-conducting. During -ve key cycle D2 conductions charging C2 to Vm. with polarity as marked, while charging C2 to Vm. with polarity as marked, while charging C2 to Vm. with polarity as marked, while charging C2 to Vm. with polarity as marked, while charging C2 to Vm. with polarity as marked, while capables of a C2 are in Series, first of vollage of a capables of a C2 are in Series, first of vollage of vollage vollage vollage approximately 2 vm. This with a cacalled full wome of blus of expectation vollage doubles because one of the open capable or being charged during each help cycle of input vollage.

Vollegi Teippler | Gradeupples

# REGULATED POWER Supplies:

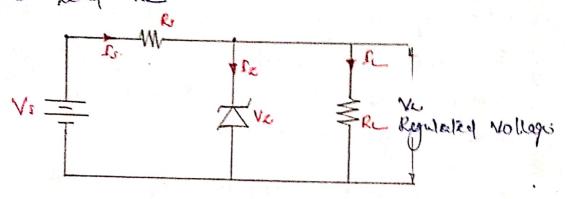

# Kenis Vollege Regulation:

Renn about Volleges regulated in a Christ-Regulation became Reservice in consected in prealled exist load. The revisional Res in cuest to limit Consent is the cett Regulated op vollege in Obtained areas load Re

Vo: [Ro+Vz. -- a); Ro. Vs-Vz. -- (2)

lord vollage YL = Vr.

L: 12+1 --- (3)

From eqn (R)  $\Rightarrow$  Ru =  $\frac{V_S - V_O}{I_{Z} + I_C}$

Remex = Nonex - Vo ILmin + Izmen.

Remin = Venox - Vo

Threat + Family

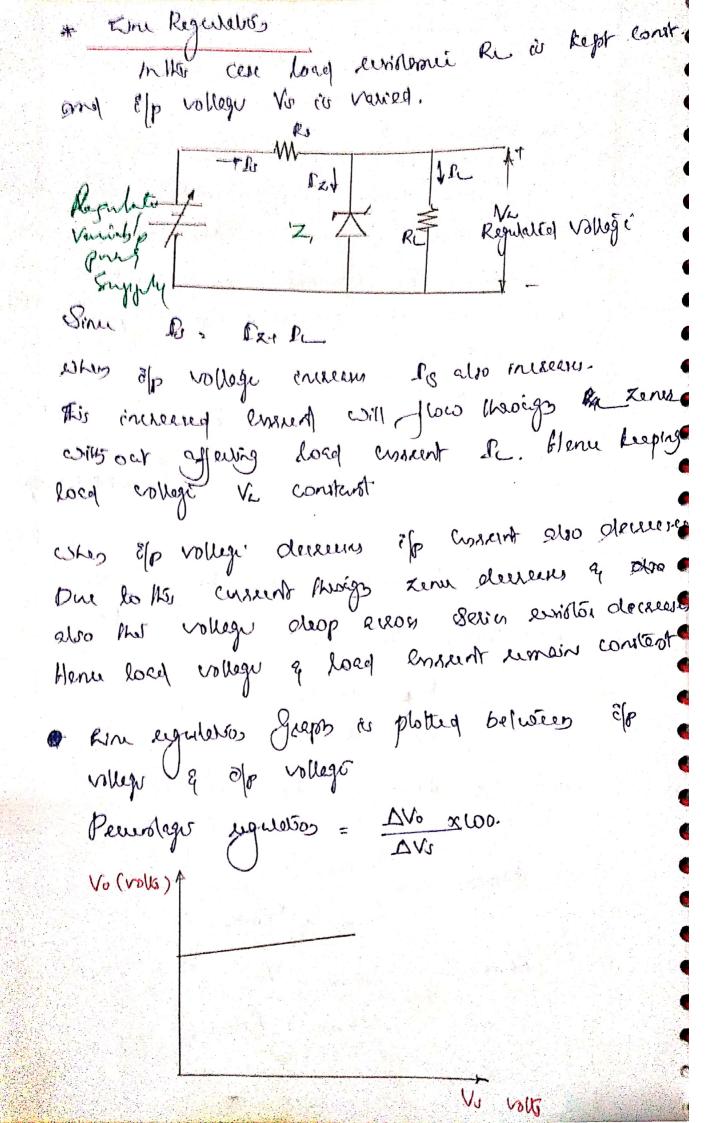

College Book Regulated college Dea Vo is kept Jined & Re a varied esting the decreen loss superat increase this court court be a decrees. .. Ve is cont. estes Re increen low Consunt dereney. Due to No Kenn Coscert increen. This egain keeps that velous of Elp consent & vollege deop secon & 2) contr : op vollage remain contr loca Republico Grepo es platea esto loca Charent or a exis of ob copped so down. Penentey engelelés: VAL - YFL × 100 V0 6016) . # It is a fixed vollege explanar & connor to mech adjustable. \* Leeze pour gets élempeléel à voire, ensoloi R \* lossesponding to large changes is local customs that costs to large changes is zone Consent. The evelle in large pour werlege

: Shurst Hollege Regulator Using Trompictors A shunst vollege equilebox using spo hamistai & Kenn dock à Orows. Rue is connected in The vollege actor local is fixed by zene diode and Oevies wills input Remidia base-emitter vollage Voc Vo= VZ+VBE = Vio- P. RSE Bine bols V2 & Vac amain nearly constant Voule remains consteat. y input volley inverse I will inverse and mused best Connect les should in intered collemni Consent Ic. keeping Ic constitor and their by Nour const. Reven Lappens when Capaly vollege develor Pe increus and when Re develor Pe increus and MG, cheremal Pc is Suppolied by decreen is I's good constraint Ic. .: I remain constraint Ve is content and : Vous is also mient Since Wis consent . Reverse Lappens when bood RC increases.

Á

· Perces Uslege Regulator.

(2)

Contiol - Rigulation Op in regulated Vollage Kliment Jampling Comparadoi Reference The bank homeelies of Olivis vollegé egulelai de Thous. The Sever element controllo the amount g'enpair vollage that get to op. The op Vollege ie Sampled by a Cher Men peovider feedback vollège to be compared la expanse vollège \* y of vollage incluse the comparation the provides à control Oignel de canu duies control element To deven the amount of alp vollage. This by \* y hur of vollege devien, hur comparelor det mandersing of vollège peovider à control signel la cense Sever control element to thereon this amount of op vollage. L'orilles follower Sever pan Regulation:

coofignation in known as pass transition because of the consent amplifying peoperty. I transition

Here their is sens doods is orall. and Hene their is bittle doop grow doods vollage tune appointable on ideal conditor vollage. There appointable on ideal conditor vollage. Francistan Q, iothe Oviv cooker) plansent and Erne vollage. The section is gothern. Recorded provides is follows. \* It of vollege amount, invened box protter Vollage cours l'émissair Q, de condent more there by saising Op vollage - mainting of containt \* If the ofp Vollegi inseries, the durient has by reducing of vollege. - mainting of p contract. Desir pan hamistar Vollege Regulatión. Yeur per limiter Contial Ro.

Contial Ro.

Contial Ro.

Contial Ro. Book and Hun the contiol orothogic lumition Q2: emplée leinnines in commented to -ve lumines of Gently Moigs zene doch

The vollege england employe the person -fudback to Vold of vollege simon constest. Q, is the part framerites became all local avon R2 is also inchem This came inchem to ensuent four Mouge et ben bies of P2; as a lunt B2 and Ic2 incluse. Dousing to constat, Po, decrees. Deven is best enauent of framillon. Que cause in care in collector - emille existence of Que. Pie cancer in enseen in Vois, and effecting that increase in Olp vollège. There ols rollège remains constent. Reven keppen when the op vollage decliese. \* Controllée hémister deux Regerent with Overload \* a Chart Cient protection. R5 = 12 In Q Vin Load terminels are shorted accidently a very lege assent oil for it cht; it may distroy hus pass liamister Q1.

codemil with prove Cussent Congres eter & edded to clearly signisted. The Current limiting extr consists of liamister to and resider R5. conseiled blo base and emitter of Po. With vormal local current de remains of because the vollege deep accour R5 is small. Under the condition extruorks nouncily. coins excersive local marent [exceeding 0.6=0] OI 6000A] The vollege deep evens R5 is enough to Lives ON latinister Q3. The collection consumt of 93. Jose théorge Re dureeing bese vollage of Q1. This lesults is reductos of conduction level of 91. There Justien increase in load auxunt is prevented touse désignéros reson pass l'amistes Pr= (Vin - VOE) ISL to told back Current Rimiting: ₹R, Vin

pours distiplies in Vision par transfer of while the pours distiplies in Vision par transfer of while the fold back out bound of a broad by Vollage obvious who of is a far the love consent. It flows things having her country deep establish. Thus Vollage of (Ichs+Vous) arts arrans (in a far) who. The vollage applied to bear of its country and is a country to bear of its country and in the vollage of the good in

VG3 = P= [SLR5+VOLY] = K. [SLR5+VOLY]

Notes = VB3 - Vous = & [I\_R= + Vous] - Vous

V653 = K [LR5 + (R-1) Vont

Now if book extensis designed, lock consists of the source of the source

increase to a local could be surrence Very increase to a local content of gets Colombia. Now collected consent the bear consent for fulling duction in the collection no effect on Its. The colorigation local consent them is

Simma: Vers : (E-17) Vont

Beyond this point Noves deaps she to adjustion with bed entirant RC=0 Vout=0. Cor - Noca Should loss current for 10 much less than temps providing fold back content briting. lord residence Rc Of Cherent But : There Turninal Vollege Regulation: Vollage Rigulation can regulated de Elp vollage Block seprendation of 3-ferminal Vollage regulation.

Fined voltage enqualate to an emergented de éty -6-Voltage approved in one êty luminal enqualied of Vo of permised and sed luminal connected to 300 and.

Tixed the Vollege Pegalelies: [78xx Sever.]

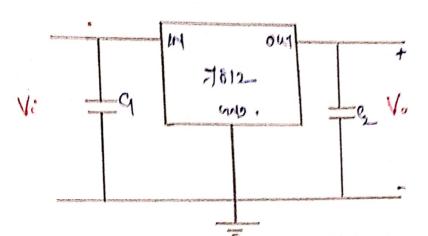

Perica 18 enjundos provide find enjund volleges from 5 V 10 24 V. 12 7812 corporated Elp Vi is applied. fillient by capacita G and consolid to 10's M learning 10's our terminal possions eigenful +124. 34 learning our connected to ground.

| 1c part | Of Vollege Vo. |

|---------|----------------|

| 7805    | +5             |

| 7806    | t6/            |

| 7808    | + 8            |

|         | +10            |

| 7812    | 112            |

| 78 15   | + 15           |

| 78 18   | +18            |

| त्र २५  | 424            |

tu Vollago Regulators in Horrs Sever.

| fixed | -ve | Vollegu | Regulatores: | ヲ9xx | Sevies |

|-------|-----|---------|--------------|------|--------|

|       |     | • #/    |              |      |        |

The Geria 79 xx provides -ve Volleger (segulded). At the provide eigensted of from -5 v to -24 v.

| Pc part | Op Vollegi V |

|---------|--------------|

| 7905    | -5           |

| 7906    | -6           |

| 7908    | -8           |

| 7909    | -9           |

| 7912    | -12          |

| 7915    | -15          |

| 7918    | - 18         |

| 7929    | -24          |

: Adjurteble Vollegé Regulation:

IC 723

The total weeky can expland by dividing it into liso store Represent Voltage Generally land Erect configur In the expense Vollege Jenerlie , a Kenne doch in bus compilling to opened of a find point by a consider cultural Journal when come clay wis- as applifue to Senade a cont vollage of 7.150 st Know emp' deliss conting exem com seria pan terminal and a compare the old vollege applied at invaling input luminal and Vey approved or Non-invalling input terminal and Vey approved or Non-invalling input terminal. Terminal. Conductos of hunista 9, is costabled by error agnel. 9 9, controll ofp vallège.

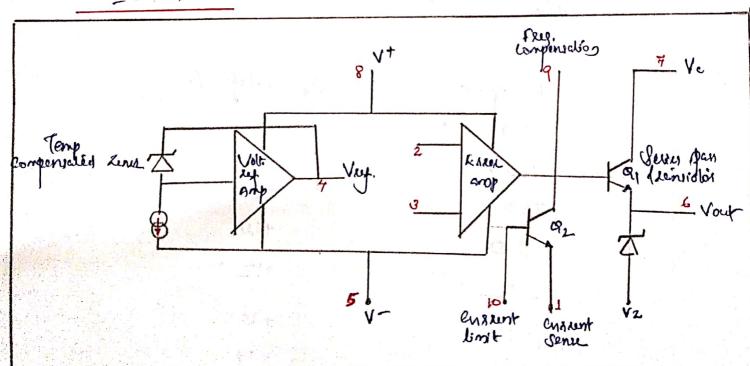

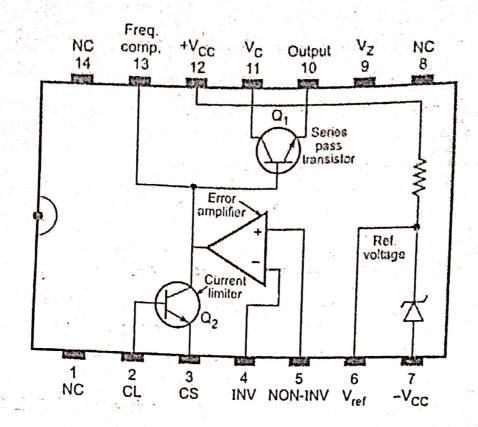

The functioning of the above blocks can be explained with the help of a simplified functional block diagram of IC 723 as shown in the Fig. 7.44.

Fig. 7.44 Functional block diagram

Temperature compensated zener diode, constant current source and reference amplifier constitutes the reference element.

Key Point: In order to get a fixed voltage from zener diode, the constant current source forces the zener to operate at a fixed point.

Output voltage is compared with this temperature compensated reference potential of the order of 7 volts. For this, V<sub>ref</sub> is connected to the non-inverting input of the error amplifier.

This error amplifier is high gain differential amplifier. It's inverting input is connected to the either whole regulated output voltage or part of that from outside. For later case a potential divider of two scaling resistors is used. Scaling resistors help in getting multiplied reference voltage or scaled up reference voltage.

Error amplifier controls the series pass transistor Q<sub>1</sub>, which acts as variable resistor. The series pass transistor is a small power transistor having about 800 mW dissipation. The unregulated power supply source (< 36V d.c.) is connected to collector of series pass transistor.

Transistor Q<sub>2</sub> acts as current limiter in case of short circuit condition. It senses drop across R<sub>sc</sub> placed in series with regulated output voltage externally.

The frequency compensation terminal controls the frequency response of the error amplifier. The required roll-off is obtained by connecting a small capacitor of 100 pF between frequency compensation and inverting input terminals.

1 + \*\*

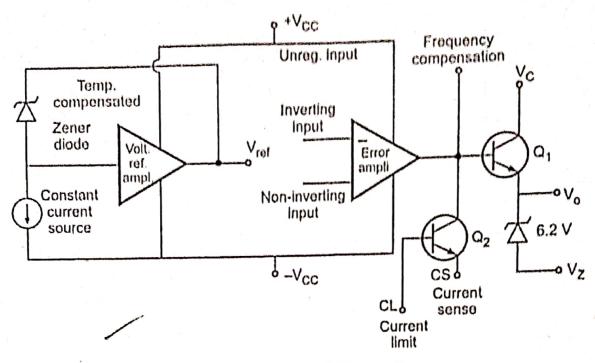

The internal structure can be represented in more simplified form as shown in the

Fig. 7.45 Simplified internal structure of IC 723

Both noninverting and inverting terminals of the error amplifier are available on soutside pins of IC 723. Due to this, device becomes versatile and flexible to use. Only restriction is that internal reference voltage is 7 volts and therefore we have to use two different circuits for getting regulated outputs of below 7 volts and above 7 volts.

### 7.14.3 Specifications of IC Regulator 723

The Table 7.2 gives the electrical specifications of IC 723. In the Table 7.2 some of the specifications are specified depending upon the application area of IC 723. There are two application area namely military grade applications and commercial grade applications, denoted namely by M and C.

| Electrical Spe                                                                              | ecifications |  |  |  |

|---------------------------------------------------------------------------------------------|--------------|--|--|--|

| Absolute Maximum Ratings over Operating Free-Air Temperature Range (Unless otherwise Noted) |              |  |  |  |

| Peak voltage from V <sub>CC+</sub> to V <sub>CC-</sub> (t <sub>w</sub> ≤ 50 ms)             | 50 V         |  |  |  |

| Continuous voltage from Vcc+ to Vcc-                                                        | 40 V         |  |  |  |

| Input-to-output voltage differential.                                                       | 40 V         |  |  |  |

| Differential input voltage to error amplifier                                               | ± 5 V        |  |  |  |

| Voltage between noninverting Input and Vcc-                                                 | 8 V          |  |  |  |

| Current from V <sub>s</sub>                                               | Special Function Ic |

|---------------------------------------------------------------------------|---------------------|

| Current from Virgo                                                        | 25 mA               |

| Content Hom Aned                                                          | 15 mA               |

| Continuous total dissipation at (or below) 25°C free-air temperature      |                     |

| J or N package                                                            | 1000 mW             |

| L package (see Note 1)                                                    | 800 mW              |

| U package                                                                 | 675 mW              |

| Operating free-air temperature range : µA723M Circuits                    | -55°C to 125°C      |

| μΑ723C Circuits                                                           | 0°C to 150°C        |

| Storage temperature range                                                 | _65°C to 150°C      |

| Lead temperature $\frac{1}{16}$ in, form case for 60s, J, L, or U package | 300°C               |

| Lead temperature $\frac{1}{16}$ in. form case for 10s, N package          | 260℃                |

### Note: 1. This rating for the L package requires a heat sink. Table 7.2

The Table 7.3, gives the safe operating conditions of IC 723. These conditions a provided by the manufacturer.

|                                                                        | Min                | Max | Unit           |

|------------------------------------------------------------------------|--------------------|-----|----------------|

| Input voltage, V <sub>1</sub>                                          | <sup>2</sup> 9.5 \ | 40  | · , <b>v</b> : |

| Output voltage, V₀                                                     | 2                  | 37  | V              |

| Input -to-output voltage differential, V <sub>c</sub> - V <sub>o</sub> | 3                  | 38  | V.             |

| Output current, Io                                                     | ,                  | 150 | mA             |

Table 7.3 Recommended operating conditions

## 7.14.4 Applications of IC 723

The various regular circuits as per the requirement can be achieved using IC723. So of them are discussed below:

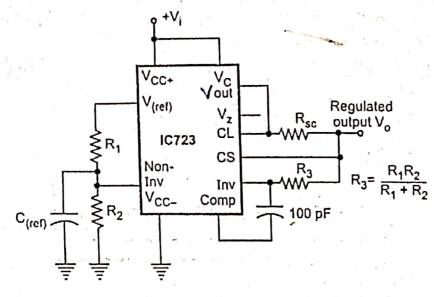

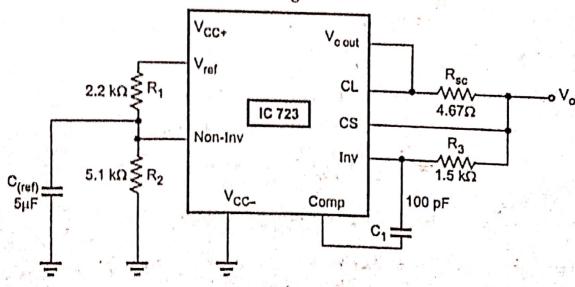

## 7.14.4.1 Basic Low-voltage Regulator (V<sub>o</sub> = 2 to 7 volts)

The resistor, Rsc is connected between CL and CS pins. The current limit transit remains non-conductive unless drops across Rsc is 0.6 V (equal to VBE drop). The value Rsc can be found out by following equation

$$R_{sc} = \frac{V_{sense}}{I_{limit}} = \frac{0.6}{I_{limit}}$$

Junit can be selected as 1.2 to 1.5 times the maximum load circuit. Potential divi made up of R1 and R2 is connected between Vret and non-inverting terminals.

$$V_{\text{non-inverting}} = V_{\text{ref}} \times \frac{R_2}{R_1 + R_2} \qquad ... (2)$$

As the series pass transistor is working as emitter follower.

$$V_o = V_{ref} \times \frac{R_2}{R_1 + R_2} \qquad ... (3)$$

Fig. 7.46 Basic low-voltage regulator

$R_1$  and  $R_2$  can be between 1  $k\Omega$  to 10  $k\Omega$  .

$$R_3 = R_1 \parallel R_2 \therefore R_3 = \frac{R_1 R_2}{R_1 + R_2}$$

Maximum load current can be 150 mA.

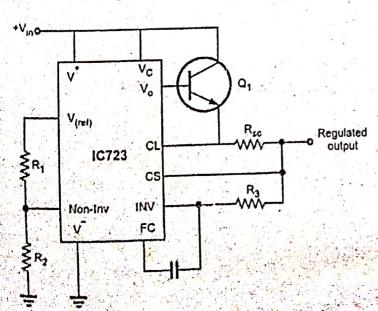

## 7,14.4.2 Low Voltage High Current Regulator

Fig. 7.47

Output voltage from +2 to +7 V and load current can be more than 150 mA. For this one transistor is connected externally, shown as  $Q_1$  in the Fig. 7.47.

... (4)

The functional equations are similar to that of basic low voltage regulator circuit.

$$V_0 = V_{ref} \times \frac{R_2}{R_1 + R_2}$$

$$R_{sc} = \frac{0.6}{I_{limit}}$$

Power dissipation of transistor =  $[V_{dmax}] - V_{d(min)} \times I_{U(max)}$

Power dissipation of IC =

$$\left[V_{i(max)} - V_{o(min)}\right] \times \frac{I_{L(max)}}{h_{fe(min)} \text{ of } Q_i}$$

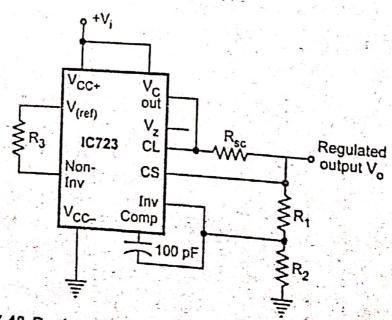

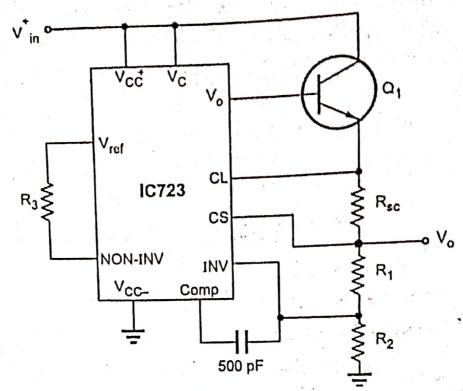

## 7.14.4.3 Basic Positive High Voltage Regulator

For this type, output voltage varies from +7 V to +37 V and  $I_L \le 150$  mA.

The non-inverting terminal connected to V<sub>ref</sub> through R<sub>3</sub>. Due to this arrangement gerror amplifier acts as non-inverting amplifier.

The gain

$$A = 1 + \frac{R_1}{R_2}.$$

The output voltage is,

$$V_o = V_{ref} \left( 1 + \frac{R_1}{R_2} \right) = V_{ref} \left( \frac{R_1 + R_2}{R_2} \right)$$

$$R_{sc} = \frac{0.6}{I_{limit}} = \frac{V_{sense}}{I_{sc}}$$

$$R_3 = R_1 \parallel R_2 = \left(\frac{R_1 R_2}{R_1 + R_2}\right)$$

Fig. 7.48 Basic high-voltage regulator (V<sub>e</sub> = 7 to 37 volts)

This is also called basic high voltage low current regulator.

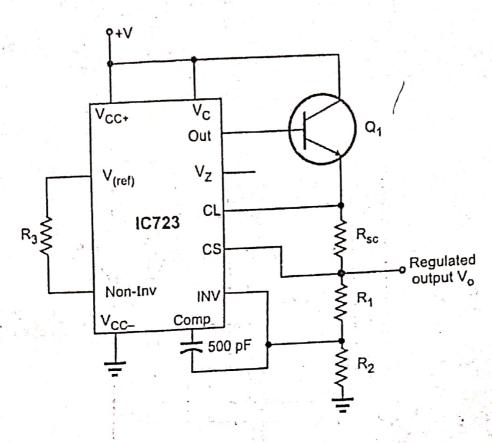

1.14.4.4 Positive High Voltage High Current Regulator For this type, output voltage from +7 V to +37 V and load current I<sub>L</sub> > 150 mA. For his a external transistor Q<sub>1</sub> is connected, as shown in the Fig. 7.49.

Fig. 7.49 Positive high voltage regulator

For this different expressions are similar to basic high voltage regulator and reproduced for the convenience.

$$V_{o} = V_{ref} \left( \frac{R_1 + R_2}{R_2} \right)$$

$$R_{sc} = \frac{0.6}{I_{limit}} = \frac{V_{sense}}{I_{sc}}, \quad R_3 = \frac{R_1 R_2}{R_1 + R_2}$$

popper a street ceeeeer While the power dissipation of transistor Q1 and the IC is given by the same expressions as given by the equations (5) and (6).

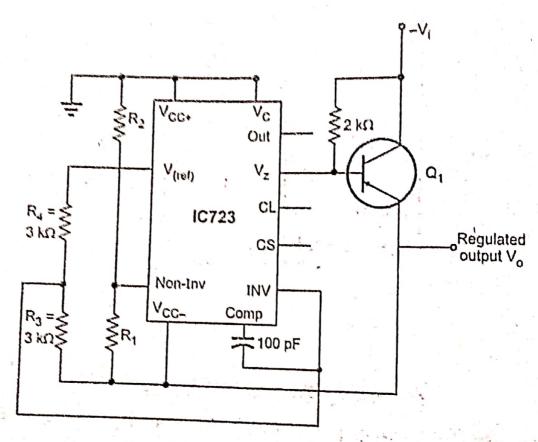

## 7.14.4.5 Negative Voltage Regulator

Connections for getting negative voltage regulator are shown in Fig. 7.50. An external PNP transistor,  $Q_1$  is connected. Resistances can be from 1 k $\Omega$  to 10 k $\Omega$ .

If magnitude of -V, is less than 9V, connect Vcc+ and Vc to a positive supply such that Vers to Vec, is greater than 9V, for proper functioning of the IC.

Fig. 7.50 Negative voltage regulator

med Example 7.10: Design a regulator using IC 723 to meet the following specifications:

$$V_o = 5V$$

;  $I_o = 100 mA$ .

$$V_{in} = 15 \pm 20 \%$$

$$I_{se} = 150 \text{ mA}; V_{sense} = 0.7 \text{ V}.$$

Solution: The given specifications are

$$V_0 = 5V$$

;  $I_0 = 100 \text{ mA}$ .

$$V_{in} = 15 \pm 20 \%$$

$$I_{sc} = 150 \text{ mA; } V_{sense} = 0.7 \text{ V.}$$

1111111111111

$$R_{sc} = \frac{V_{sense}}{I_{sc}} = \frac{0.7}{150 \times 10^{-3}} = 4.67 \,\Omega$$

Neglecting input bias current of an error amplifier we can write,

$$R_1 = \frac{V_{\text{ref}} = V_0}{I_0}$$

where

In = potential divider current = 1 mA

and

$V_{tet} = 7.15 \text{ V for IC } 723$

$$R_1 = \frac{7.15 - 5}{1 \times 10^{-3}} = 2.15 \text{ k}\Omega$$

Use 2.2 kM standard resistance,

Now

$$V_{ii} = V_{iel} \cdot \frac{R_2}{R_1 + R_2}$$

$$5 = 7.15 \cdot \frac{R_2}{(2.2 + R_2)}$$

$$2.2 + R_2 = 1.43 R_2$$

$$0.43 R_2 = 5.11 k\Omega$$

Use 5.1 k\O standard resistor.

$$R_1 = R_1 || R_2$$

=  $\frac{2.2 \times 5.1}{2.2 + 5.1} = 1.536 \text{ k}\Omega$

Use 1.5 k $\Omega$  (standard) resistor.

The designed regulator is shown in the Fig. 7.51.

Fig. 7.51

Example 7.11: Draw circuit diagram of IC 723 based positive voltage regulator, to give 12 V at 500 mA output. Incorporate short circuit protection limit circuit to operate at 600 mA, Find all resistor values calculate their wattage and specify the type of resistors,

Solution:  $V_0 = 12 \text{ V}$ ,  $I_L = 500 \text{ mA}$ ,  $I_{sc} = 600 \text{ mA}$

It is positive high voltage high current regulator as shown in the Fig. 7.52.

Fig. 7.52

Now

$$V_{o} = V_{ref} \left( \frac{R_{1} + R_{2}}{R_{2}} \right)$$

$$12 = 7 \left( \frac{R_{1} + R_{2}}{R_{2}} \right)$$

$$5 R_{2} = 7 R_{1}$$

$$R_{1} = 4.7 k\Omega$$

$$R_{2} = 6.58 k\Omega \approx 6.8 k\Omega \text{ standard value}$$

$$R_{sc} = \frac{0.6}{I_{sc}} = \frac{0.6}{600 \times 100^{-3}} = 1 \Omega$$

$$R_{3} = R_{1} \parallel R_{2} = \frac{R_{1}R_{2}}{R_{1} + R_{2}} = 2.7 k\Omega$$

Power wattage of  $R_{sc} = (I_{sc})^2 R_{sc} = (600 \times 10^{-3})^2 \times 1 = 0.36 \text{ W} = 360 \text{ mW}$

All the resistor type can be of metal film resistors. For the power rating of R1 and R2 assume the input current to the inverting terminals zero.

$$I = \frac{V_0}{R_1 + R_2} = \frac{12}{(4.7 + 6.8) \times 10^3} = 1.043 \text{ mA}$$

$$P_1 = I^2 R_1 = (1.043 \times 10^{-3})^2 \times 4.7 \times 10^3 = 5.112 \text{ mW}$$

and

$$P_2 = I^2 R_2 = (1.043 \times 10^{-3})^2 \times 6.8 \times 10^3 = 7.397 \text{ mW}$$

So both  $R_1$  and  $R_2$  can be selected safely of  $1/16^{th}$  watt power rating.

## FIELD EFFECT PROMUTORS:

estico dependo for it operatos os the costál of consent by an Electric fiera.

There are two lips of FETS:

(9)

\* JPET.

\* MOSFETS [Insulated Gate FETS].

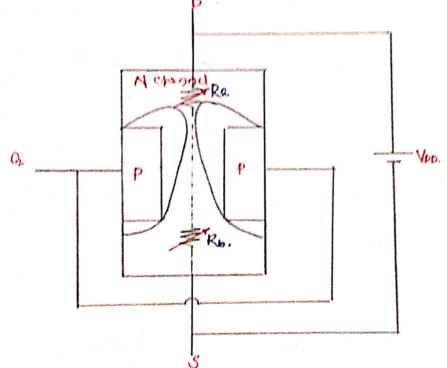

# : Junciós Field Effeut Teamiolox:

P- channel. to No. Chremond supplies N- channel and P- channel. to No. Chremond supposed supposed consumations

The 3 learnings of offer see Sale Course and Deers. Sale is controlling learning. Socre is the learning through which charge carriers and the device and deals to the learning through which device are carriers and through which device are carried through which change carrier leave the slevice.

Operation of Jet Depution Loyal formations to Jet

Hen Plepi Get et Milipi Channil

Constitute a pri junitation This pri junitation Channel to

rement branch strang Tres Operation. In a reverse

brased Junious Man exists olipletion region entinds to the

composite ions. This deputies region entinds to the

exists where disposing consultation is Low.

Vollage ocean Drois & Source.

In this channel ese can assume libro channel desirable the personal open to person the person the person to person constitute the Charent the Charent the Charent the Charent the Charent the known as Desir charent the Chare

Here depletes legios in not Symmetrical became of that fact that severe vollege in higher near the decis and compared to Dance and of crossel, decis and compared to Dance and of crossel, appears that liso depletes region could louis earn one and is referred as fines of the vollege at which this happens is called pines of vollege up. At which this happens is called pines of vollege up.

Too with meximum skeep consult for JET and in Ordined by the constition VW = 0 & VOS>(Vp) The Vollege You can be used to control the strain consisted the Strain Consisted for JET.

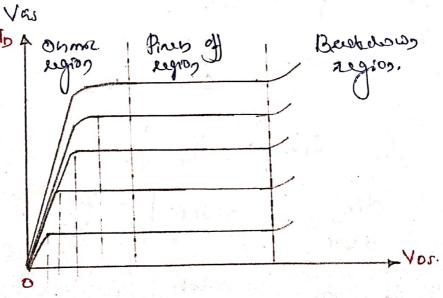

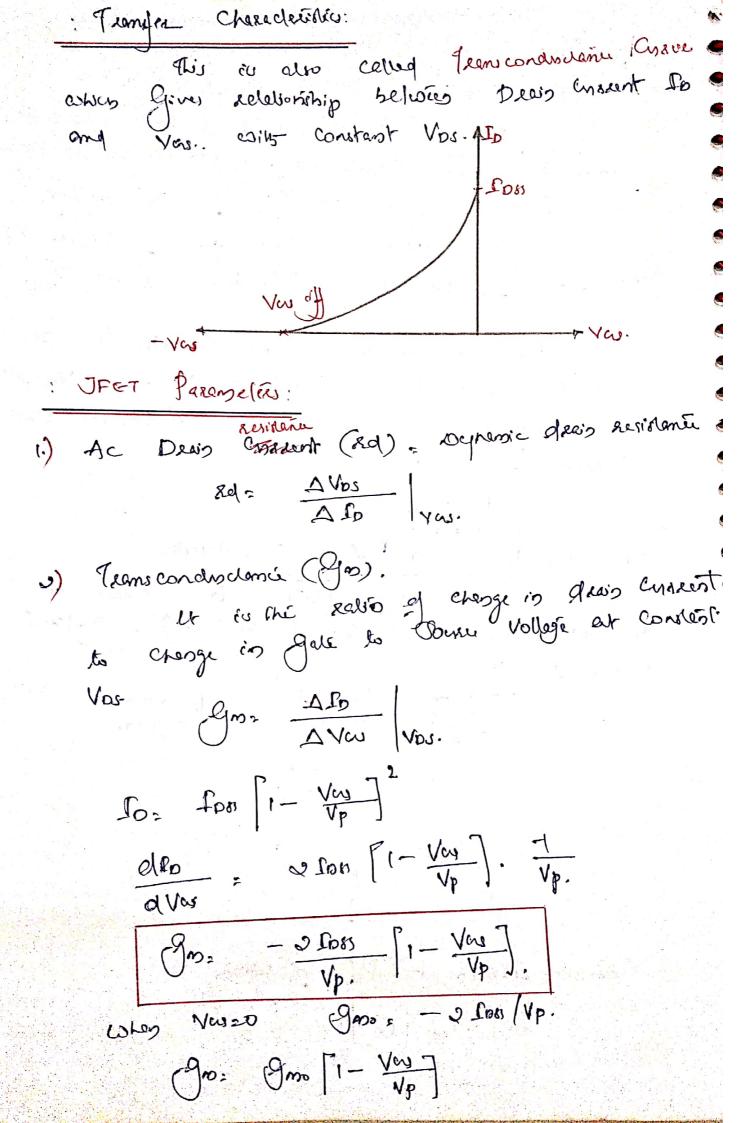

\* JFET Characteristics \*

VI Cherculeriolis Or Deas Characteriolis:

It is the Greek platted between Dewis Conseent To and Devis to Soner Vollege Vos. - for obijerust value of Vas

Jo 4 onma , Pines of , Berekerson

Conseent relation at Pinen of region

To: Toss [1- Yus ] => Behackley's equation

s. Volley Controlled device

3. High ilp impediate (MR)

5. Higner (Spilching Upred

Cremate les noise

7 Ocupies les Grace is la

8. power consignos is loo

nusno

hele vollage controlle skur

Megalini limp coefficient

conductos ocus due la bob è q holes \* ensure Coolishy olivice

Bose Consunt cookedle collection CHRRINT

\* los ils insedence (t.s.)

\*Positive lemp coefficient

Lower Obsiling Open

\* Chemiels mon noise

\* Occupies mon Open is Ic

\* Digh power consamples. \*

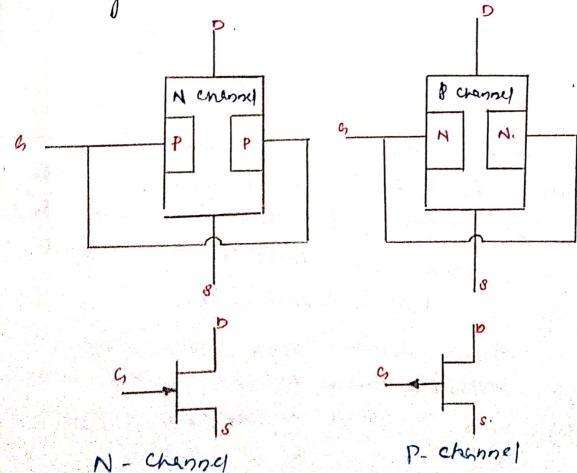

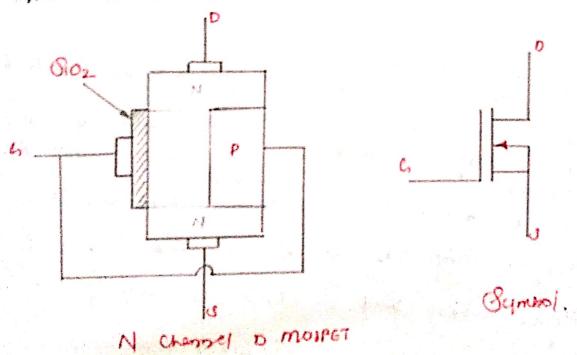

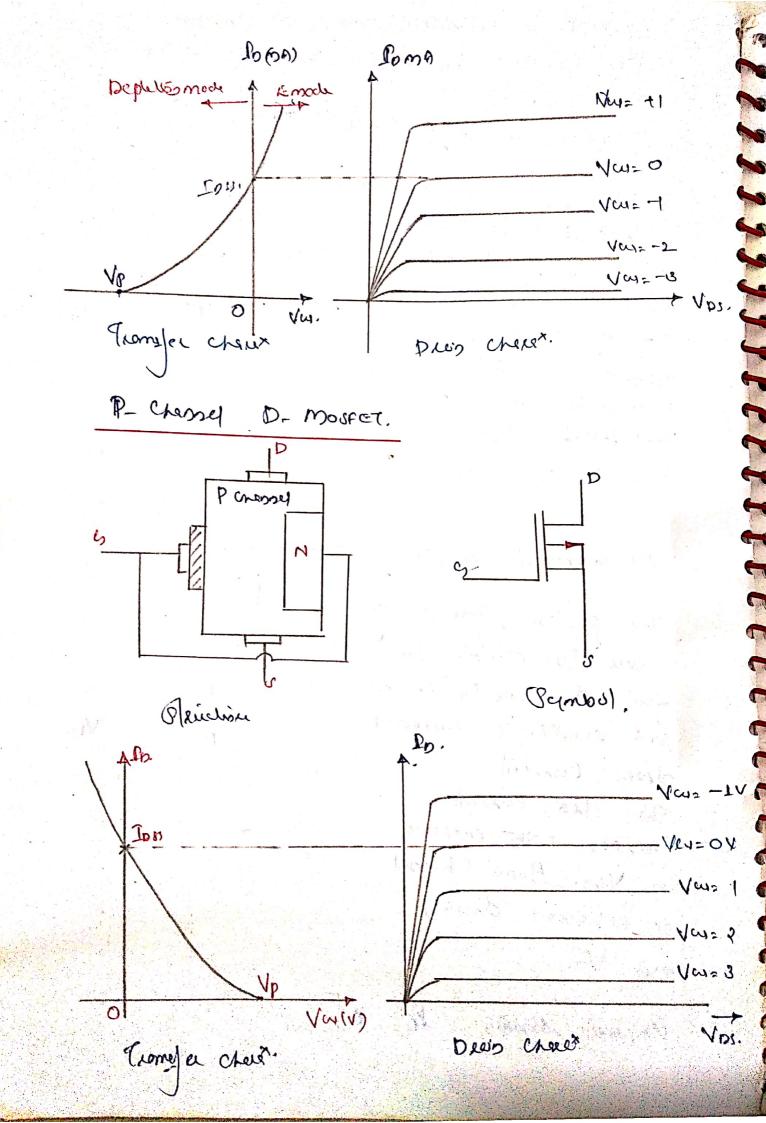

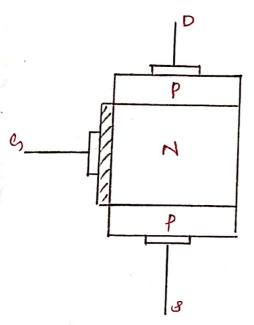

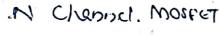

mosret & also celled & Mulcled Coette

Fet (raper). Then is no obsert electrical content

before for & channel of mosret. One to the

pureous of Insceros (me 510) believes get &

channel mosret pasen your fight ip impedence.

and there is no get content!

MOUFETU are of luss light depending on whether

the channel in almosty print or not,

\* Depletion light moufet

\* Enhancement lype moiset.

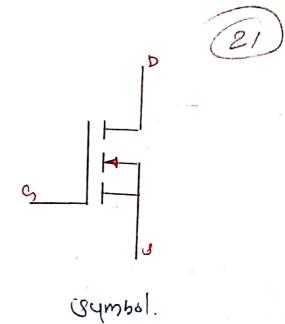

## D-MOSFET

their exists an inhuent channel.

Operation Vouso and Vos is applied the Decine of Course. The result is alterities of Einschennel and altering Toward the potential of Drain learning and alterin

mocern in course petalosses is tressed. and pulse is a sery their of themself site 0 1) DEEL. expects mod of Operation The to we want our VI bull charact work in trails igete and of chancol. Nepopol. This Other to deduce the Vps. Ş. Effective courts of Otenosi gry this sedmen the constration. I the. and theifou Devis ensunt Duran. Enhancement mode of Openboo. The positive gali vollage came Jus efection to move N Change! from Jaboleshi la channel and resulting is increased Val. P duis county. This days consumt increase esist increase in Vos. Honu Chansel T Vers

Comment states for the

is enhanced during

the Ves.

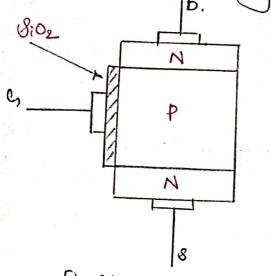

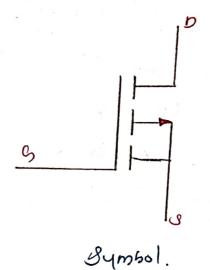

In E-MOIFET, there is no inheart channel. It can work oply is renhancement mode

P Chance Mosfet

Operation

In Emospet Their cis

no inhunt Channel.

Poy the application of

the Vas it will

althour E la the

gold and of maspet.

and there by create a layer of e estich Creels a channel bles Deus 4 Gower. ID= K[VW-VWH] Vwgn isher Yollager et which channel is creded The Jali to Oomen Vollege required to credé a channel believen Jours & Drain and this to links ON the lumisolis in known as Theeshold Vollage So. VW=V1=12V. Temple Charex Desig Charax.

The bows function of humilian is Amphification.

The percent of saising the Signed Steength of a creek digned without any change in its general shape is known as - faithfull amplification. For faithfull amplification it is receivery that

- 1. Dex L'emilla Bare jemels of surard biand

- 2 la jundios Revenu bissed

- 3. peoper zus signel collators Consunt.

The people flow of Zero signed collection answert Ic and membersone of peoples Vois obving parties of signed is celled Transition biaring

Bian slabilization:

Bies chebilizelión.

Only fixing of Operating point is not Gayfreent, if must also present that it should earner that when it was fixed.

Then are his event for speeding point to Orth.

\* Temporal gain an lengthering dependent to me parematic such as a energy from emit to enough.

The maintenant of Operating point stable (independent of temperature Novichios and Vasidions is transition parameters in knows as

Flow of Connect in collection Current Circulation of Connect of edition clet this chewer that lemperatein and more monopolity carriers are generated to bene collection junctions. Virus more bonds one beaten and resulting letters constituted for finalities.

Ic = BFB+ (B+1) Icho.

menan is Icho increase Iceo to and this is they increase collection consumt of Ice authoritation computative increase is Ice authoritation computative increase is Ice will cultimately shift operating point. They even hear processes at jumpinos and this even bury the hamillois. Such silvidios is even bury the hamillois.

Operating point & oc lose line.

Ton propose Operatos, of liangillar, which the Oignal (ar input) is present on not a fixed level of engineer and volleges are regulared. These Volleges are regulared. These Volleges are required to Volleges are repoint as which volleges a point as which will point it celled the laminais operator. Quinent point.

Almyring EVL 10 of OKL Vee Ick - Vee so. ego O canhe equally to ego for a line J= Pc; M= //Re a= Ver epo @ define a lone de= 0.; Ver Ver Verso Re: Veepe The less volves see less ends of Slope = - IRC Operating point De bord line DC load line can be defined as a line on Op charelevilles of liamentar which gives values of Reso vignel fe and Ver cossupondry lo condition. toe loved line five following information local line intersects The howgooded love axis ar a point need vu which is called

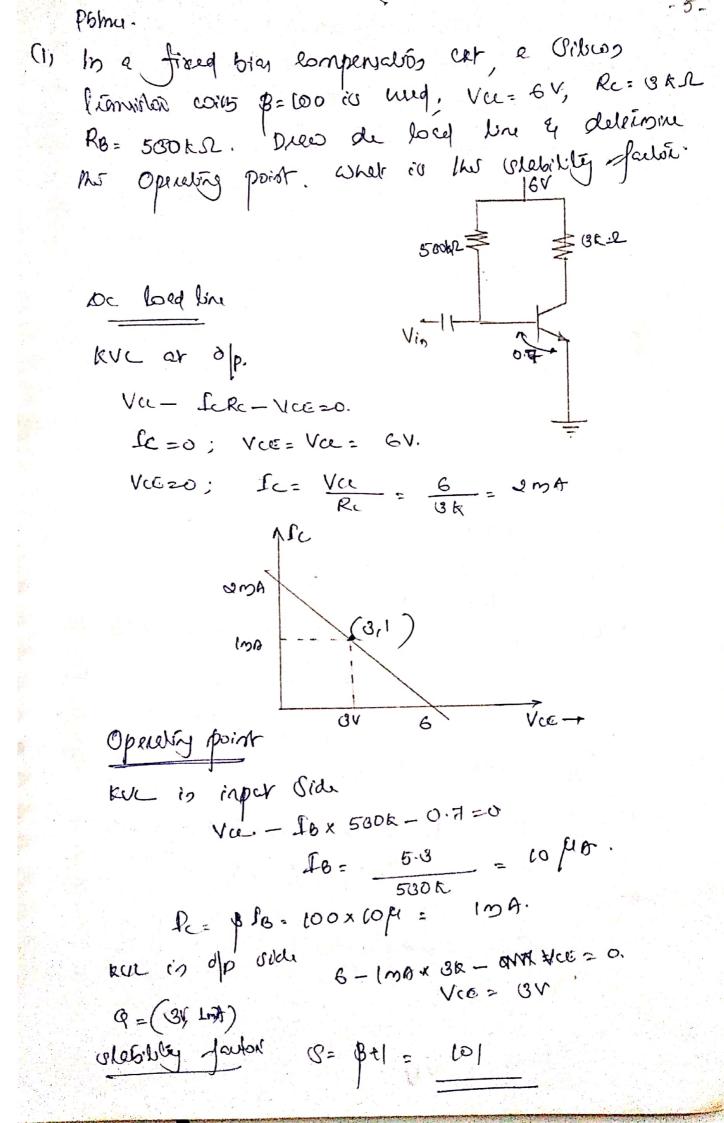

Kennistas cutself point. At this point de Esta-is The local line institució viented artes et pointe meeted ver is called Gatherster point. OF this point the is maximum & Ver = 0. stability ofelow: slobility factor is is defined as he Reli g change of collabol content 60.8.65 Ico tisping B & Vace Combot. Dec= les Ic = \$PB + (PH) SCBO. le = Blo + 971) Ico. ... 0 Differentiating ego @ w. 1. 50 de 1 = B ale + Bill Deco (pti) des = 1-18 des S= ORe = (B41)

1-BORB 1-B DRB

or low line;

me at load line gives the Valnes of Vale and he when ar vignal is appointed. At load line teles into account, this ac local elevidance able de loag line concidées to only de loca divirtance.

This means to its constaint a fined Utability - factor for fixed bias cor ere Lave Ic= BPB+ \$71) Ica. 1 = B DRB + (BAI) DRC Bow LB iv independent, of E. A coint fixed bigs chet, it is easy to fix designed to fixed bigs chet, it is easy to fix degrees. of the chart by Bimply changing the value of existence Ro. It provides meximum femility is design.

4 freed Bias Chr i'v reldom ment temperature collabor Cyrrent for goes on inevening of their by ineversing lemp again & come theirs Running. \* are know R=BIB; Men IB is fired,... Circunt le is volety depend on B. estes Promittoi in represed by another one with different volne of B operating point will origh. The orlabilization of operating point in very pool.

The chir is well who collected everymice Re to vry Omall.

The Connent is emillie Re Courses Vollage deap in a direction to revenue bear the emillie base joinchos for homista to emais in article legion E-B promotos has lose proceed biased, the enquired big is obtained from power Capply through polished divider Mw Right.

I le levies to inneer due la inneer is Ico vits l'imperetire vollège desp aux Re invives there by dieneriss ban consent Is. Oo Ib & & Re maistained as almost

YICRET)

Co, Crives his volleges divided bles Chir, believed & points NY RI= 50 RA, K2= 12.2 RA, Re= URA, Re. 100 M., VCE = LOV, ; VOEONE O.HV, B= 150 222 26.1 56R wer. 12.26 = 400 R 56 RN 12.26 = LOKIL Wx 12.20 12.26+56R = 1.79V KUL is ilp side 1.794 - Sog LOR - 0.7 - (BATIS x 400 = 0. 200 100 - 151×400] = 1.09 Jog = 15.48 MB Ica = 2.34 M 1. Pcq = 15.48x (50 = 2.32mA 10-2.Kx 2.32m-100-0,34mx400-0 KVL to op Vcaq = 4.424 Vie 5mA (4.424, 2.32m) CON

AF pomplifice

Rr boplifice

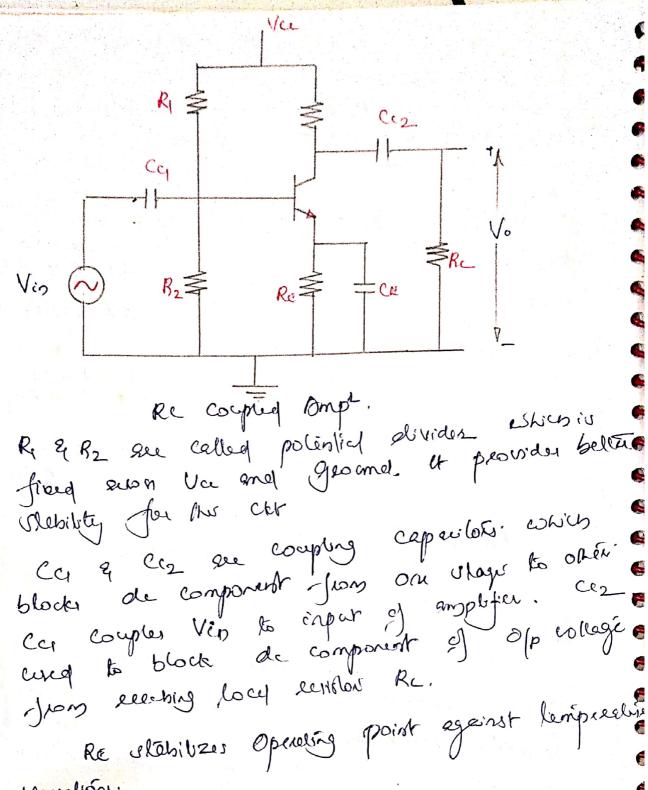

## : Rc Coupled Amplifier:

It is a Cir amplifier and for coupling of amplifier of a compression of a

Vauslions.

le isther by pan caperston which bypon se Vignel developed across Re la georne, The receloné of cer should be much less thes Re XCE X

Flequency Response of Re coupied Omphilia -7 Feynmay supranu of an amplifu come Gup. prolling believes Jupuny (x-arr) of gos (4-ens). The Did Juliana Bond Widt Sugarsey Ju to the figurey response play con can dee gain ong constant gos at mid Juguencies. of low Jupanies, loaping capeuloss les q Clz will be Very Ngn [xc= 2010] and their more is signed and vollege will not couple propuly to supplied and hus amplified of will hot couple peopledy to local ... going reduces at low furcenies capacitomés and strey winns capacitomis plays capacitomis and sole is endury the gais. Of a moson sole is endury the gais. Of set high Jequences this capacitomis will set

es Short cht : Sp signed will be Charled la ground before it recens amplifier and that ofp of amplifier also should to ground before it recens to board : Join will reduced at high frequences, but his effects compensate of mid-jupanues there has effects compensate seembled to give content gain.

Hen the Banqwidt of an amplified is defined as the renge of suprenses over winds that amplified provides desired gais.

BW: - JH - JC

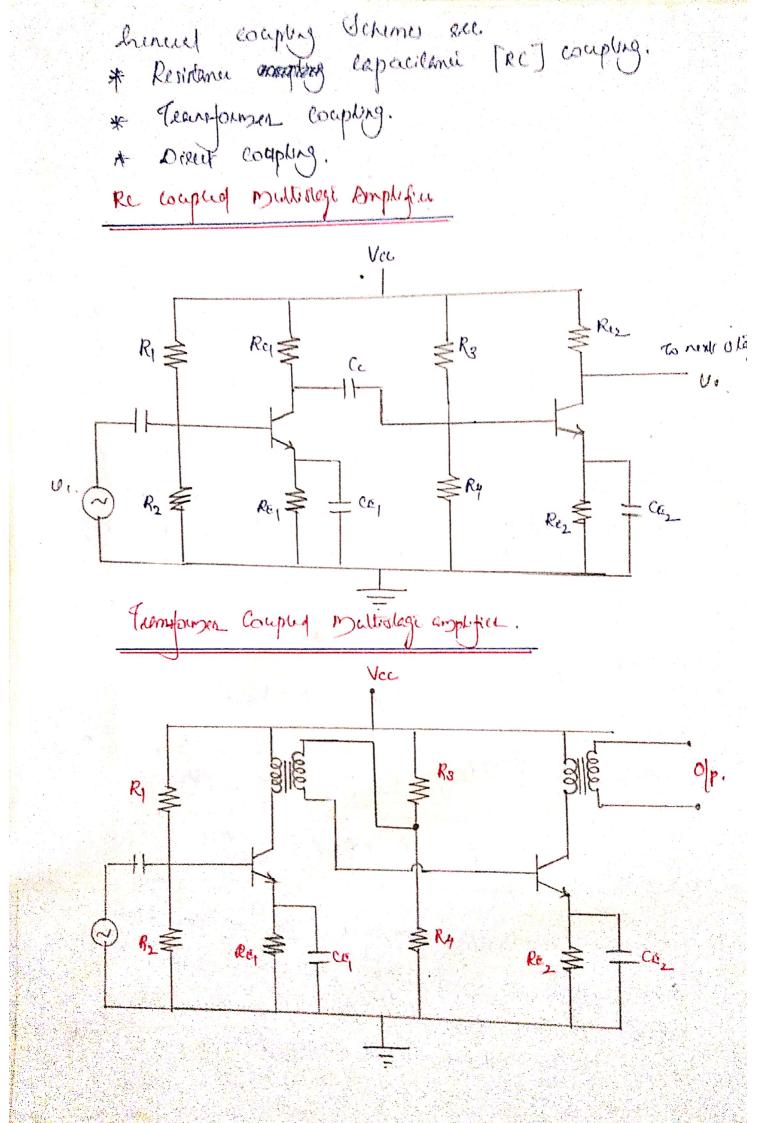

soliquate, his first can be investigated by considering there on college of smplification. I considered there is called mellistics couplification.

Us. A N B2 12 50

How he stage makes input of 3 to stage and to come of the Cignel Us is experient to the imput of the stage of the old of the stage of the Cignel Us is experient to the imput of the stage of the stage

de of 24 degre 1/2 = 1/2 0,

ful of vo= vo= 10-Vo-1

Over all gest A= 100 = 1/1 x 10x x 10x 100 100

A = A1 × A2 x --- An

In a multivillege amplifier of glore orders, make input of new orders, con must one a excepting nelicion believes too stage that a minimum loss of Vollage Occasi when Gignel person therigh the relicions to new orders.

riffer of Cascading on Join and Banqwidts.

In a Multi vlegé amplifieur a number of vollegés gass.

Ale eascarded to Obtain Lynn value of Vollegés gass.

Y an 'n' slages au cascaded the Over all midband vollegé gass becomes

Au' = (Aum)?

esheu Aum ister midband Mollege gass of isdividuel slage.

But Bandwidt of the amplifier doubt remain the Came, Bandwidts; will derevery whereasts and lower cutoff fuguency derevery and lower cutoff fuguency derevery measures. It happens because Gerelia in runture of capacitais in number of capacitais in number of capacitais in number of capacitais in runture of capacitais in the coesit. and seek capacitait affects the frequency the coesit. and seek capacitait affects the frequency the coesit. and seek capacitait affects the frequency according a covered of the coesit.

y fi & Je see lower and upon culoff , the own all cury frequency Jespennies of individual Mage -So! = V 315 -1 - J2 fugury is 1/2-FRED BOCK AMPLIFICES: The vollage gain, input & output impedinces ond Bondwicks et se jew important characteurs constent and for an amplifier and all enguseed to be controlled. This is achieved by feedback. Feedback to a furthigue is which a past of

or a Jeanton of output is connected back to input

When the feedback applied as to include the -10input Signal, it is called Positive on Direct or Regenerative feedback

when the feedback to Go epplied as to deceses the input Oignel, it is called Negative on Invence on Degenerativi feedback.

Feedback in Amphifien:

960 = A 961 Ds. 24 = B20 feedback N/W (B)

A feedback amplifier essentially consists of los parts. \* On amplifier \* A feed back Neltooks. The finelion of feedback who do lettres a fraction of of energy (vollage on Current) la input of amplifier creatly it is made up of sessible, includes on capacitions.

Negdrée feedback Ri= QJ-Bro. A = 20 |20

aco = Aal = A[21-820] 96 [1+AB] = A Rs.

Ay = 06 = A 1+ AB.

$\int_{A}^{A} y = \frac{\alpha_0}{9u} = \frac{A}{1 - A\beta}.$

## Keller of Negative Jeedback on Amplefieur.

Eventhough the amplifier goin is sedned estité pegaline feedback, réjetue feedback employer this performance of emplifier Jeon Comany other points of

The reductions of years advantages of -ve feedbank ell \* It improves to chability of symplifier good. Ur leanus his distailing and noise.

ar includes input impedence It seduces output impedence Ut increases Bond Wills

Zain Otability

gain with -ve feed 5 ack AB>>1

Cline B is the feedback gain which depends only on polive component Ocech as lititles when are fined; the gain costs - feed said as almost stuble. Rednus Oinabos on Noix

y so rulle de Rolling wingour feel back By, IN distables coils feedback Thes

Mu distribution is reduced by the clame factor as the

Inexerce is input impedence Zi = inpar impedent collesour feedsab with perdocale 34 = inpur improvenu MG Rij = Ri (1+AB) is oxygur impredence Deckely To = Owbat impeding without Jeed 5 wile outfut impedente with Jerdbark thes Zoj = 20 1+03. Inclose in Bond width BO = Bandwids collinar Jeelsack Buy: Band willy with geedback Baj= BW (1+0\$) Reduces the Locon and Jeyensey Negative feedback hereas apper ent of Jenney ; lower cur of Jung J2 = J2 (1+0B); cupper cury) Je4 Sais BO: -52 - 51

Moder N DSULLATORS Chrisication · Osulalor Pinnoidal Mos Pinewords Bign freg - Aslable M.V - RC phone Shift oscillator Monorlable m.y Wein Bridge Oscillatol. Cupical Or8 Bislable M-V. Penuph of Oscillatos Oz Certerios for Oscillation 26 No= Axi Ampli fee MIXING deld buch 2 px

Aleu amplifier provider an ofp Vigner No: Axi - Seed back Signel 2] = Bao = - 1821 From figure ofp of mixing Cht: -al. I g'= xi coe can connect agl as input of the instead of all For their condition to be validied 1AB| = 1 4AB = 0° 01 860°. This is celled Brekhawan's Criteria Osvilations le clemified is levins of this outpu coareform, fey earge; components or cht configure y output coave-form in Simulaided et in called Vinespieles Oscillator Obucon cally Relexation Oscillators which include Govern restangula and Vaw book wareforms.

Flow from it can be noted that Vio it collectly At of value of amplifice. Vous & values econ Rece act as Juniback vollage Ur. ges, of Janban 140 \$: 4 hat he imprediou of Jewin connection of Rici The coffestive impostume of 11th Alo ReC2 Vr = R1 x Vin  $\beta = \frac{\kappa_2}{\kappa_1 + \kappa_2} \qquad (7)$ Now x= R1+ 1 jωq 72 = B2 = 100 1+ 10 C2 B2 B2 + 1002 B2 H:500282 Rub! S: 10. 1+ UR2C2 1+URC1 + R2 1+UR2C2 JG B2 (1+URIC1)(1+SB2C2)+UR29 SCIRL 1+ UB2(2+ SR(C)+ SR RRLC(C2+ SR2 C)

SG B2 1+0 [ RC1+ B2(2] + 02 R1 B2 C1 C2-+0 R2 C1 SGRZ 1+3 [RC1+R2C2+R2C1] + 3 [R1R29(2] 0=10 & 03 = - con 1+ jo [RIC1+ R2(2+ R2C1] - 02 RIR2 C1(2 1-02 R1 R2 C1 (2+ ) W [ R1 R1 + R2 (2+ R2 C], Mallypy with comprex conjugating Dz on N2 & Dz. : B= jo 482 [(1-12-12-12)-jo (R14+ R2(2+R24)] (1-62 R1R2 G(2) 2 W CR1 4 + Re(2 + R1 C1) Equale inaginary part to Reso. 100 GRZ (1- W2R1BZG(2) = 0. 62 R1 R2 C1 (2 = 1  $\omega^{2} = \frac{1}{R_{1}B_{2}C_{1}C_{2}} \qquad \omega_{2} = \frac{1}{R_{1}B_{2}C_{1}C_{2}}$  $\int = \frac{1}{\sqrt{R_1 R_2 C_1 C_2}}; \quad i \int R_1 = R_2 = R; \quad C_1 = C_2 = C$ Now-feedback Jallon β= ω²Rc (3Rc)+ jωcR (1-ω²R²c²) (1- 62 R2 2) + 62 (BRC)2

Equating Real part  $\frac{1}{9}$ For Owlesized Oscillosis  $|-A\beta| \ge 1$ Angelinite Glesibzolosis.

For Gustined Oscillation amphific gain A ≥ 3, this gain of amphifica Thould not be los longe as it will distort the olp wave-form.

i. amphifier gain showed be controlled.

This is achieved by introducing -ve feedback by keeping serialist Ry is emilled of a configurated.

This introduce consent bever - feedback. This introduce of gain seduction using -ve - feedback is known as amphibility slabilization.

Hartely Oscilloloi in a High Jeyway (RF) -4-Oscilletos exces coses los indendoso la a capacitar to on this - feed back Alas which devides the Jupuscey onlyo Mestalo Majo Maso For Unlained Osvillation has condition to be Getafied X+ X1+ X3 =0. Where M1 = WC, ; ×2 = WC2 & 73 = -1 104+ mc> = 1081ω [4+c2] = 1 σος3. J= = 1 21 / (2,+12) (3

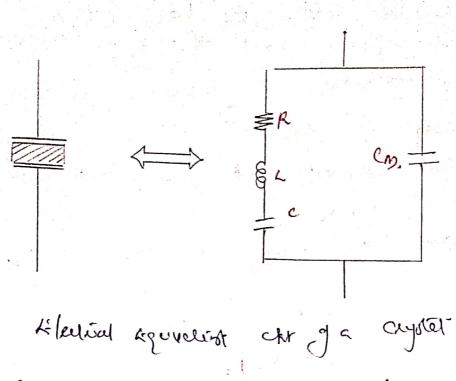

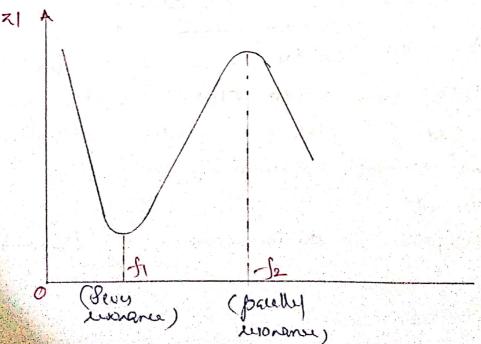

· RRYSTAL OSCILLATORS:

A central oscilloba in borrolly a bined ext Oscilloba cuing piezo electric central or seronant tenk ckt. Central Los greater relibility en Larding contant feequency to which it is originally cut to opuseli Mais approcation ser is communicated liaminilless of securior

The Crysles can have less remost frequencies. One humanst conditions owner when rechanges of General Rechanges of General Conditions of Conditions of General Conditions of Gene

at a hypen July wallow of Capaulot Ch. At kis flyword Capaulot Ch. At Kis flyword Capaulot Cht.

Hen Caystel às connected as deves element in a feedback past. It Jesses ensont mode impedence is smaller a smount of feedback (tex) is largest. Hen - RPC coil provides de bies while decoupling any ac vignel - Jeon affecting of vignel. The lesselling other - Jeopensey of Osvilation is ser by seves resonant juneary of Caystel.

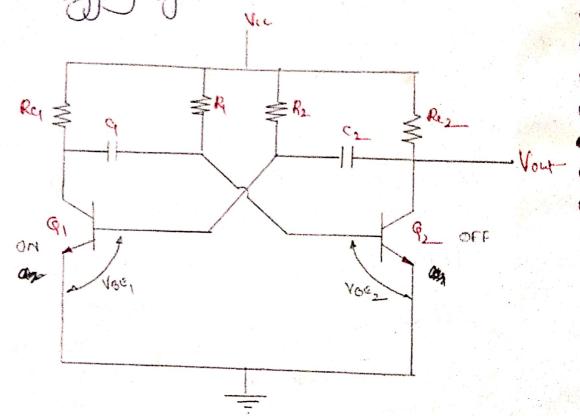

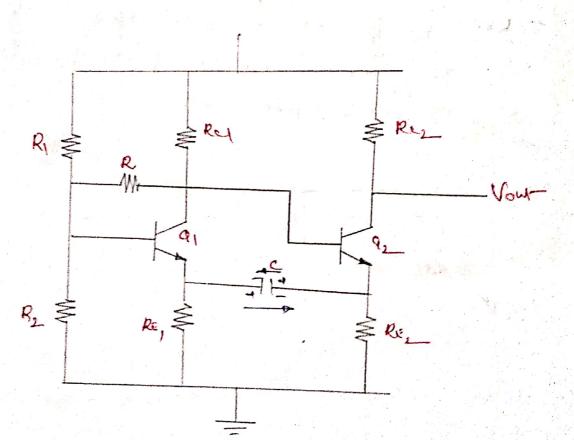

## ASTABLE MULLIVERPIARS:

It is also celled free econolog Mellinistelos. It has no oteble steles. The live steles of perebes of now are great stells (Empreony) stells The now thingou make Generally transition from one great steble other to another of the complete of the to another after a perdetermined line interval consour the old of external leigneum Closel.

When power is first applied to the circuit 6065-Premission state conducting. Beener of parametric variations, on of the Premissions constants more has other.

Let en assume Q Conducto mon Plas Q2, especially loss vollege of Q1 deops lepidly Plas Q2. Resulting loss vollege feel to base of Q2. Proigs to ceparate q and drive of to curst. Os a result of Post of the curst.

sign racounts vice are of box, of 9, and drives it to isolandies Ds soon as an other co-ducting capacities C1 Cranges Rollowers Von Mango R1. When the Vollege Scien G size byong Volenn of the or hegins to conduct the P2 to conducting, now to collected. value chop a low volley not can coupe to be basing on manys capacitor of and makes it of Now since Pe is conducting capable to Charge lowers Vir Margo Rz. who volley work ex Rikes beyond Vocans of an alest consumity and the collection voluge drops. The low voluge makes as off. and he cycle repeats. Since the take of from he collabor of one of the homeston con vicon ger a Oquan coque. CP, OH a g on Vapat Marine Chamber and Marine W relativa integralia estra